大家好、

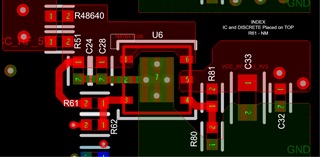

我们在 布局电路板文件中使用了 LP38692SD-ADJ/NOPB LDO 部件。 我已经附上了板级配置文件和原理图的图像。 请检查布局并与我们分享您的反馈。

我们使用的 PCB 包含12层:

IC -放在顶部

第2、4、9和11层是地线、

使能信号来自 L5

谢谢。此

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

我们在 布局电路板文件中使用了 LP38692SD-ADJ/NOPB LDO 部件。 我已经附上了板级配置文件和原理图的图像。 请检查布局并与我们分享您的反馈。

我们使用的 PCB 包含12层:

IC -放在顶部

第2、4、9和11层是地线、

使能信号来自 L5

谢谢。此

尊敬的 Teja:

我看了分享的原理图和布局部分。

您能否共享此器件的应用? 这是一个较早的 LDO、我们可能在给定条件下具有更好的器件。

是否有理由在输入端并联两个0欧姆电阻器? 0 Ω 的跳线很常见、但我想知道为什么两个并联。

该器件在 EN 引脚上没有有源下拉、因此、请确保驱动 EN 的信号不会低于 GND 电平或高于 Vin。 可以安装下拉电阻器。

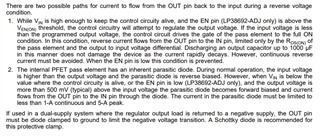

请注意、有些情况下可能会发生反向电流:

布局看起来不错、我最重要的评论是、或许较新的 LDO 或许可以提供更清洁的布局、因为输入和输出往往与较新的 WSON 封装位于相反的一侧。

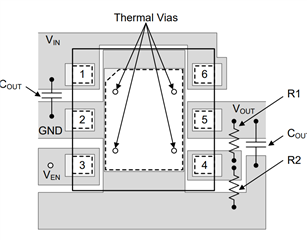

这样可以改善顶部的 GND、但总体而言、它遵循数据表中推荐的布局:

以下是快速建议: TPS746数据表、产品信息和支持| TI.com

此致!

埃德加·阿科斯塔

尊敬的 Edgar Acosta:

感谢您的宝贵反馈。

谢谢。此致、

- Teja