大家好、

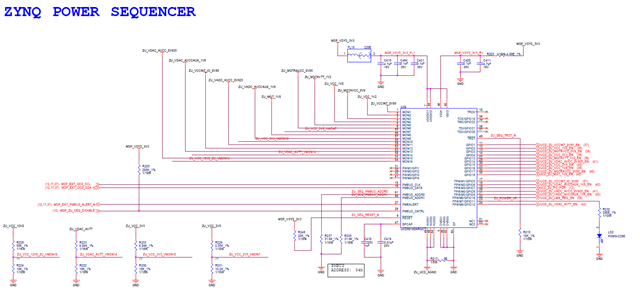

我们有一个定制电路板、其中包含 UCD90160电源序列发生器、用于对 FPGA 的电源轨进行监视和定序。 在新的定制板的构建中,我们使用了 UCD90160A 器件,这是 UCD90160的引脚对引脚替代器件。

我们有一个包含 UCD90160的设计的系统文件(.tifsp 文件)(添加在随附的 zip 文件中供您参考)。

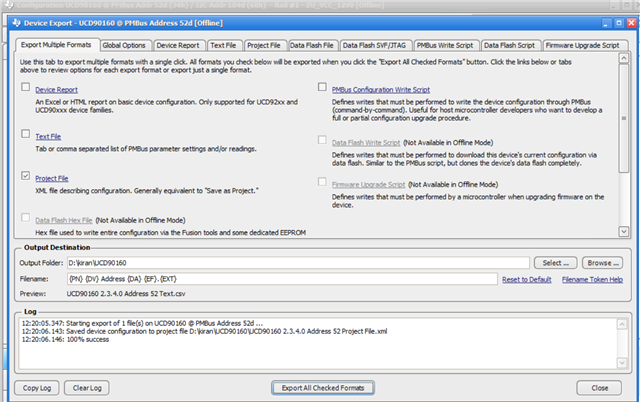

从该系统文件中、我们可以使用 Fusion Digital 工具单独以离线模式导出 UCD90160的工程文件(XML 文件)、如下图所示(XML 文件位于随附的 zip 文件中供您参考)

在具有 UCD90160A 的新定制电路板构建中、我们导入了该 XML 文件来配置 UCD。

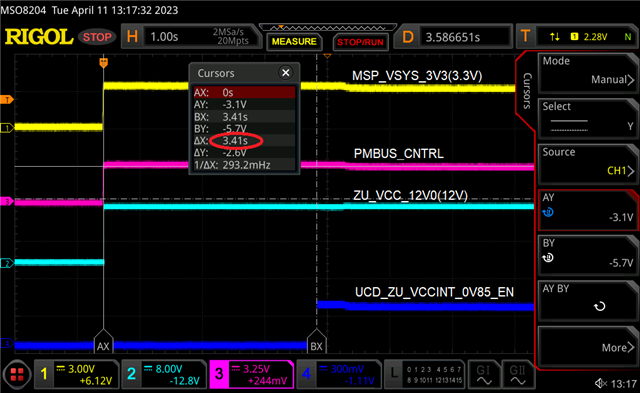

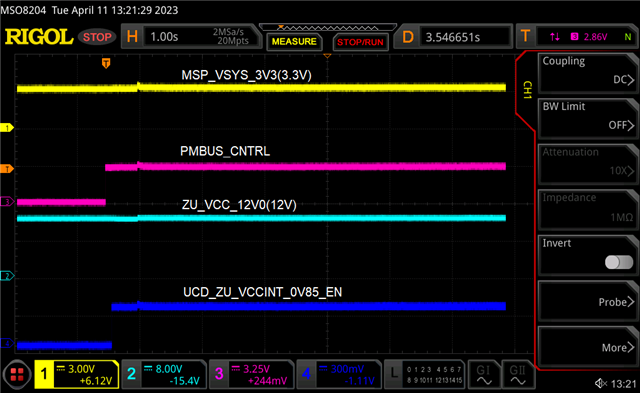

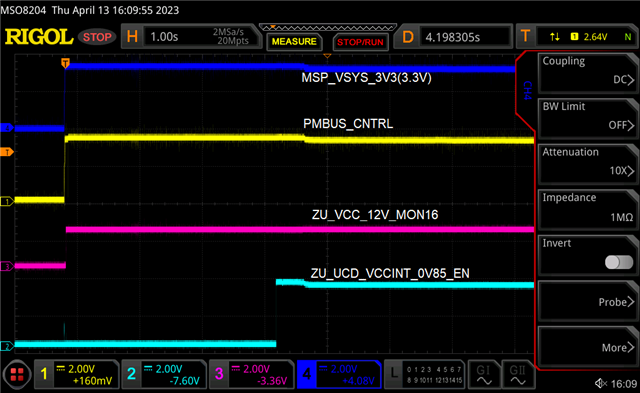

成功导入并配置后、电路板上电后、需要大约3.5秒来完成 FPGA 电源轨上电、这在之前用于立即上电的电路板中是观察不到的。 当开始调试该问题时、我们发现在监控第一个电压轨(即在我们的设计中、该电压轨直接来自外部电源)之后、UCD 将按顺序启用第二个电压轨延迟了约3.3秒。

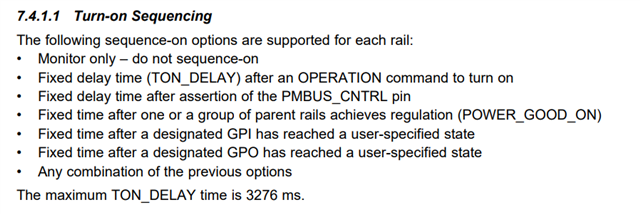

从 UCD90160A 的数据表可以看出、可配置的电源轨的最大 TON_DELAY 为3276ms、如下所示、这个值几乎与我们在上面观察到的延迟相匹配。

即使我们尚未将 TON_DELAY 配置为3276ms、UCD90160A 也会进入最大 TON_DELAY 状态以开启第二个电源轨。

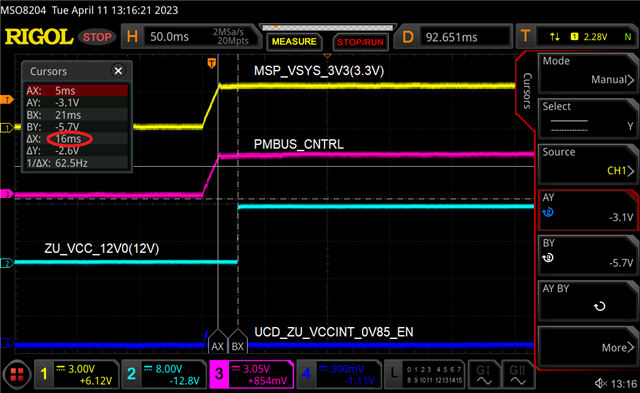

只有在电路板通电后才会观察到这种加电延迟。 当通过 PMBUS_CNTRL 引脚控制 UCD 来关闭和开启序列而不关闭外部电源时、UCD 行为正常、我们可以在 PMBUS_CNTRL 置位后立即观察 FPGA 电源轨的上电情况、没有如此大的延迟。

我们能否知道导致此类问题的原因是什么?

这是 UCD9016A 的原理图、

e2e.ti.com/.../UCD90160A_5F00_TI_5F00_query.zip

--

提前感谢

Kiran