请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS3421 您好,

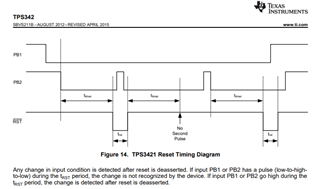

TPS4321EG 芯片、当 PB1和 PB2引脚同时下拉时、复位引脚是否会被下拉400ms? 如果400ms 后、当 RESET 被上拉时、PB1和 PB2仍然为低电平、复位引脚会被立即再次下拉还是不会再次下拉?

客户是否见数据表中的以下内容表示、即使 PB1和 PB2保持低电平、输出仍会被上拉、除非 PB1或 PB2被上拉然后下拉? 请帮助确认。 谢谢!