主题中讨论的其他器件: LM7480-Q1

您好!

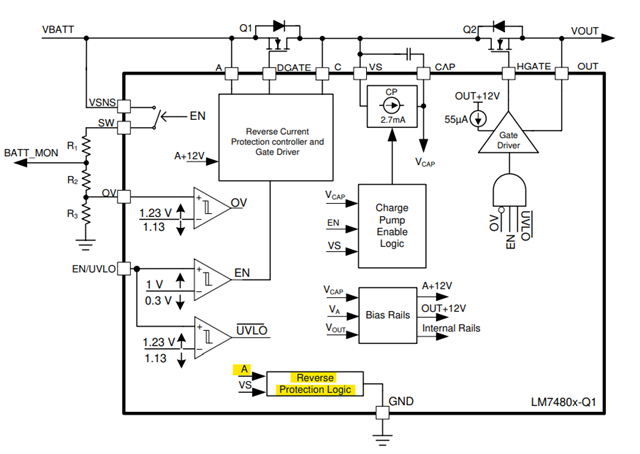

目前正在使用 LM74800设计(使用 CD EVM)、并且在某种情况下、LM74800 C 到某个电压大于绝对最大电平(>85V)。

您是否认为添加一个电阻器和齐纳二极管来钳制电压有助于保护 IC、同时让电路正常工作?

连接到 VIN NFET 源的电阻器 引脚1连接器、引脚2连接到 IC A 引脚和齐纳阳极

齐纳阴极连接到 IC 阴极和 MOSFET 共漏极

这是否会影响钳位期间的 IC 运行? 钳位将是连续的、除非 MOSFET 共漏极处的电压或输入端(MOSFET 源极)的电压被移除。

谢谢。