Other Parts Discussed in Thread: UCC28C56H, ATL431, TLV431, UCC28781EVM-053, PMP22322, UCC28781, TL431, UCC5304, UCC28782

主题中讨论的其他器件:ATL431、 TLV431、 PMP22322、、 TL431、 UCC5304、 UCC28782、UCC28C56H

您好、TI!

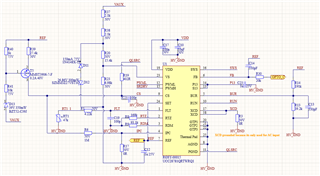

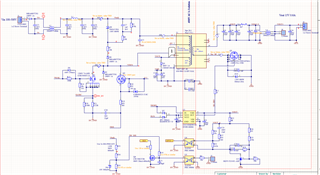

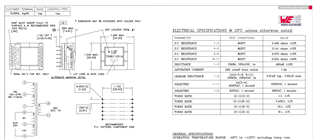

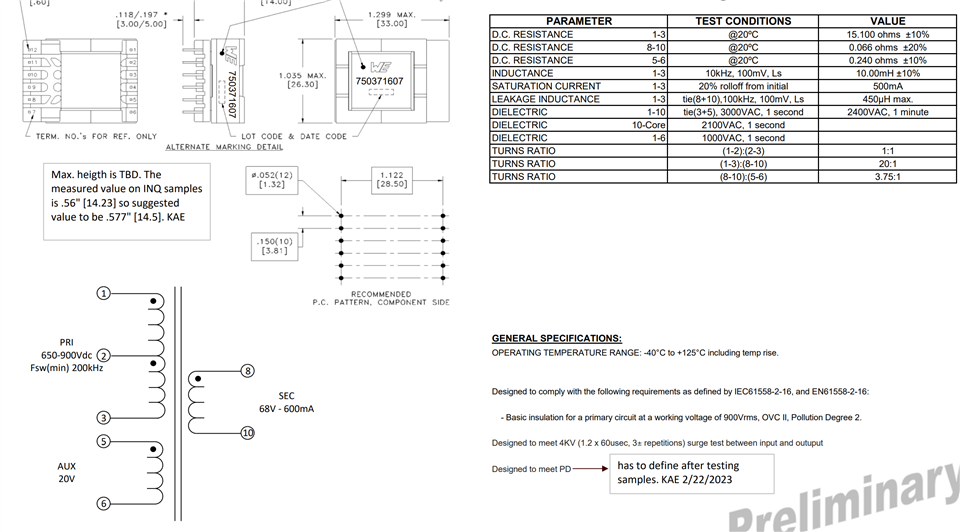

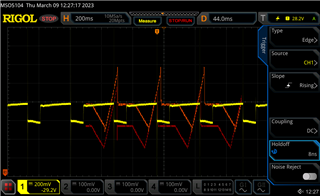

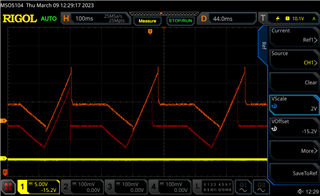

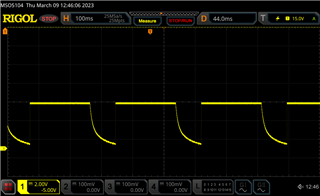

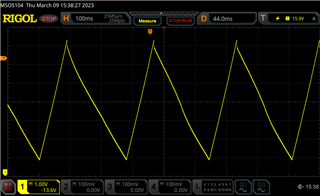

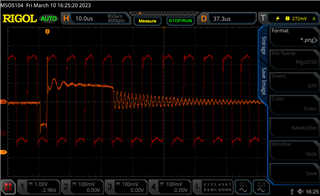

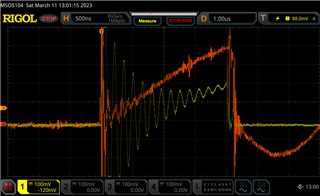

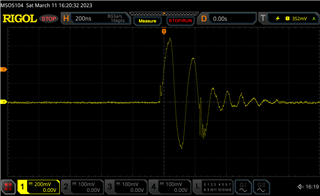

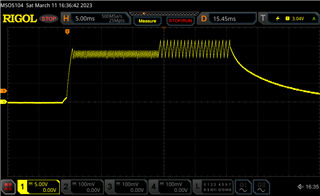

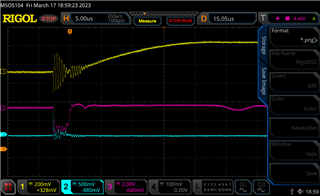

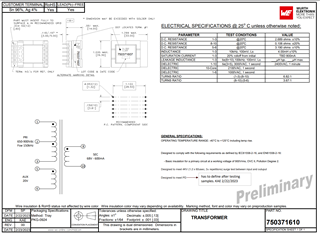

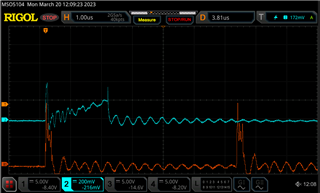

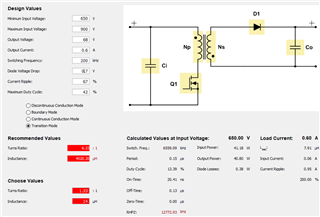

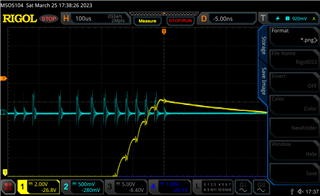

我们已经按照您的 EVM 原理图制作了一个测试板、但测试板无法启动。 定制变压器尚未制造出、因此我们使用这款现成的器件来进行尝试、引脚排列不同、因此我们使用短线进行相应连接(见所附数据表)。

我们的 PSU 目前仅提供120V 的最大电压、因此这是我们目前要测试的、但我知道该设计应该从100V 开始、对吧? 它消耗0mA。 我在15V 输出节点上放置了1k 负载。

如何解决此问题? 我们应该测量哪些节点?

电源。我们知道 AUX 连接错误、在安装和正确安装变压器时已经考虑过这一点。