主题中讨论的其他器件: TPS546D24A

您好、TI 团队、

我在 设计中使用的是 TPS546A24A。

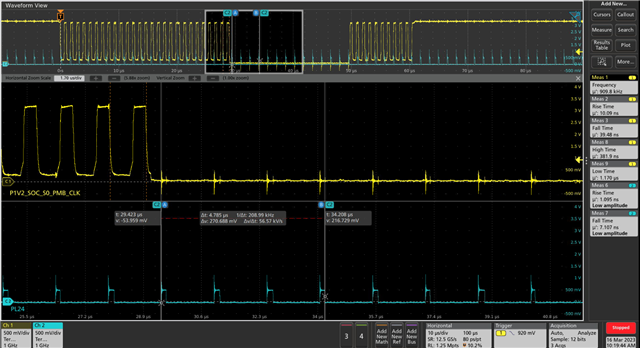

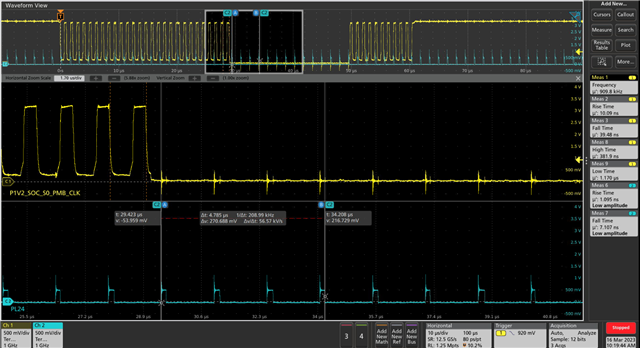

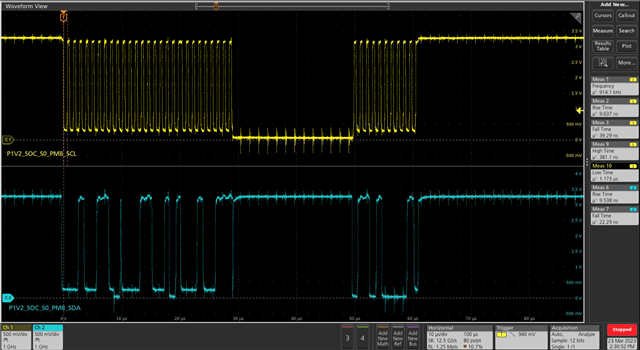

但当我测量 PMBus 时、我看到了周期性噪声、我发现噪声与开关波形同步。 请查看下图(顶部是 SCL 信号、底部是在输出电感器处测量)

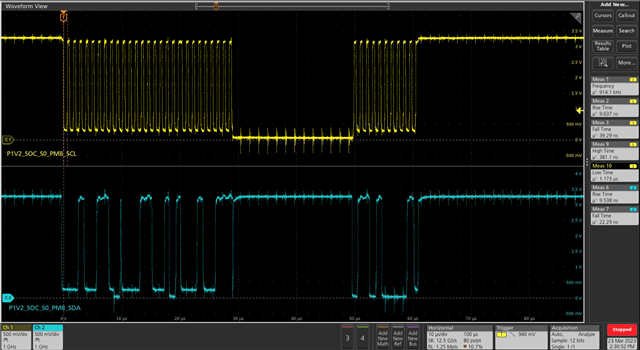

SCL 和 SDA 上的另一个图像噪声

我看到当 SDA 和 SCL 处于低电平状态时、噪声更大。

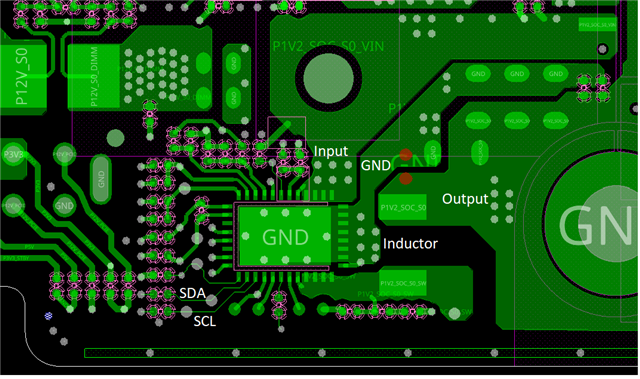

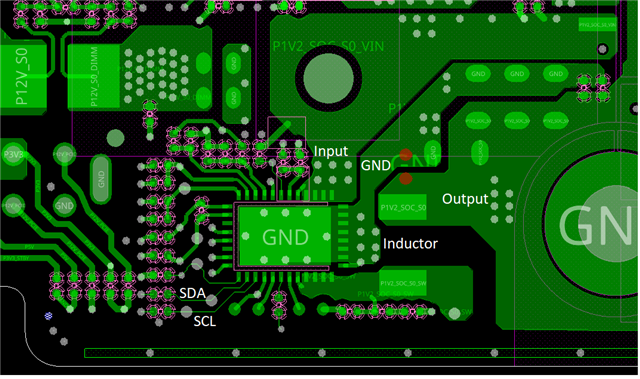

请参阅下图中的布局

是否有任何方法可以克服此噪声?

谢谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、TI 团队、

我在 设计中使用的是 TPS546A24A。

但当我测量 PMBus 时、我看到了周期性噪声、我发现噪声与开关波形同步。 请查看下图(顶部是 SCL 信号、底部是在输出电感器处测量)

SCL 和 SDA 上的另一个图像噪声

我看到当 SDA 和 SCL 处于低电平状态时、噪声更大。

请参阅下图中的布局

是否有任何方法可以克服此噪声?

谢谢。

您是否看到 PMBus 交易失败了? 您发布的波形似乎显示了一个有效且已完成的 PMBus 读取事务。

您似乎看到的是、当 TPS546A24A 将 CLK 或 DAT 引脚拉至其本地接地时、PMBus 的接地差分噪声和示波器拾取、 这也是您在运行期间的特定时间在 CLK 和 DAT 引脚上看到较低"低"电压的原因- TPS546A24A 的 CLK 和 DAT 下拉电阻比总线控制器的下拉电阻强得多。

SMBus 和 PMBus 将 CLK 和 DAT 引脚定义为要求在 CLK 和 DAT 上都具有最小50ns 的干扰滤波、专门用于防止接地差分噪声(如此开关噪声)影响测量。 此外、当拉至低电平时、当总线为高电平时、噪声需要超过800mV 或低于1.35V、然后噪声才会损坏数据传输。

我看不到您展示的任何噪声接近可能破坏交易的值的任何迹象。

但它没有通过 SDA 和 SCL 的绝对最大额定值。 正如您在波形上看到的、最低电压约为-450mV

是否发生了任何潜在的损坏?

[/报价]您看到的波形是 CLK 和 DAT 引脚、这些波形跟踪 TPS546D24A 的 AGND 电压、因为它偏离示波器的接地检测。 由于绝对最大额定值相对于 TPS546D24A 的 AGND 引脚电压、因此没有风险。

当 TPS546D24A 内部的 CLK/DAT 下 拉为"打开"时、可以看到接地噪声内部下拉电阻最大阻小于20Ω、以满足1MHz 类 SMBus 的0.4V @ 20mA 规格。

,我还有另一个问题。 如果边缘出现噪声、则会发生非单调问题。 50ns 毛刺滤波能否处理非单调问题?是的、50ns 干扰滤波器将处理 CLK 或 DAT 引脚的任何非单调上升/下降。 监控外部引脚电压的内部网需要外部引脚超过转换阈值、并在内部网发生变化之前保持超过50-80ns。 如果外部引脚恢复到其先前状态的时间超过5ns、这个50-80ns 的延迟将被复位。

从高空闲状态开始、引脚将忽略之间高电平为5ns 的50ns 低电平流。

从低电平状态开始、引脚也会忽略50ns 高电平流、两者之间存在5ns 低电平。

这是为了让 TPS546D24A 忽略其总线上的 I3C 流量。

[/quote]