大家好。

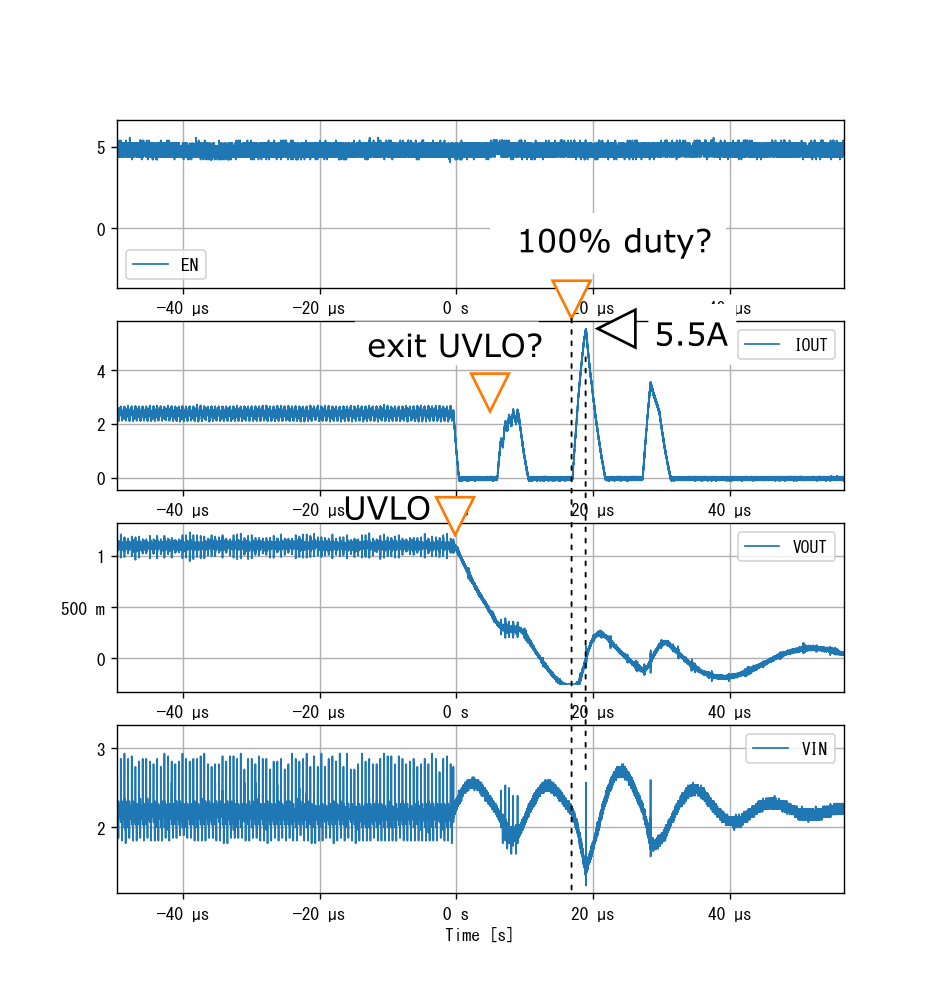

当器件进入 UVLO 而 VIN 出现严重振铃时、我会观察到 SW 引脚过流。 此器件的这种行为是否正常?

SW 引脚上测得的峰值电流约为5.5A、远远超出工作条件、并且高于高侧 FET 电流限值(最大值)。 我可以通过添加更多电容器来减少 VIN 处的振铃、但我想知道这款器件的行为为什么如此。

此致。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我忘了说、我的测试设置使用电子负载消耗2.4A 的恒定电流。 如果我将电子负载设置为消耗2.0A、则 IC 的行为与上一帖子中所示的100%占空比模式不同。 如果我在关断前通过 EN 引脚禁用转换器、UVLO 将不会被触发并安全停止。

(2.4A 负载下为↓μ A。 关闭前的 EN-OFF。)

(↓μ A、2A 负载。 探测 SW 引脚电压、而不是电流、因为我现在没有设置电流探头。)

(无负载时为↓μ A)

您好!

我认为这次对话有点失败。 我提出问题的最初目的是"该器件如何在 UVLO 之后传导大电流"、而不是"如何减少振铃"。 后一部分已通过添加电容或通过使能引脚关断来解决。 前一部分涉及到、因为我的以下任一项假设都不能满足。

1.在正常运行期间(VIN > UVLO)、OCP 最高应在5A 时触发。

在 VIN < UVLO 期间、高侧和低侧 FET 均关断。 因此、只有体二极管允许电流流动。

您能解释一下我对设备行为的误解是什么吗?

此致、

您好!

没问题、当你对该线程添加注释时、该线程会自动重新打开。

由于 VIN 正在振荡并处于 UVLO 操作边界、因此您会看到器件尝试重启的一些区域。 以橙色突出显示的区域表示高侧 FET 开启。 从技术角度而言、它不是100%占空比、因为 VOUT 为负。 此处的 VIN 只下降到了大约1.5V、这不同于第一张图片中它下降到1V 的情况。 示波器屏幕截图就会发现、如果您也向最后一张示波器屏幕截图添加电感器电流、

此致、

瓦伦

您好!

感谢您的讲解。 因此、根据之前拍摄的示波器、OCP 在达到5A 后约300ns 时触发。 我认为这比典型值60ns 长得多。 这是预期的 OCP 行为吗? 此外、首先为什么高侧 FET 为接近1.9µs 的电压接通?

在 实际应用中发生这种情况的几率可能很低,因为您需要一条长导线的过流情况才能使 VOUT 变为负极。 [/报价]您是说当 VOUT 低于0V 时、这是器件的预期行为吗?

此致。

您好!

我知道此情况很常见、但我们需要清除此问题、以便在下一个项目中使用 TPS62823。

如果 VOUT 不为负值,您在主板上是否看到此问题?

简单地将 VOUT 引脚驱动为负电平不会导致此问题。 也不会在2A 负载等稍微不同的条件下发生、如上一篇文章中所示。

此致、

您好!

谢谢你的答复。 这些信息非常有用。

由于设备在 PFM 中启动,VIN 可开启1.9us

,由于 VOUT 为0V,转换器将开启高侧 FET 的时间更长

我仍然不确定这一点。 除非器件以100%占空比模式运行、否则器件应以恒定导通时间控制运行。

此外、如果数据表仅在 VIN=2.4V 至5.5V 的范围内有效、这是否意味着当 VIN 介于 UVLO 和2.4V 之间或在 UVLO 延迟期间不能保证任何效果?

此致、

您好!

该器件中使用的 DCS Control 拓扑能够在输出电压较低时延长导通时间。 以下应用手册介绍了此 https://www.ti.com/lit/an/slyt531/slyt531.pdf。应用手册中的图3显示了负载瞬态期间导通时间的类似扩展。

我们通常仅提供建议的 VIN 工作范围的电流限制规格。 例如、当器件处于 UVLO 延迟时、由于在此期间 VIN 较低、内部传播延迟可能会长于典型的60ns。

此致、

瓦伦