主题中讨论的其他器件:TPS56221

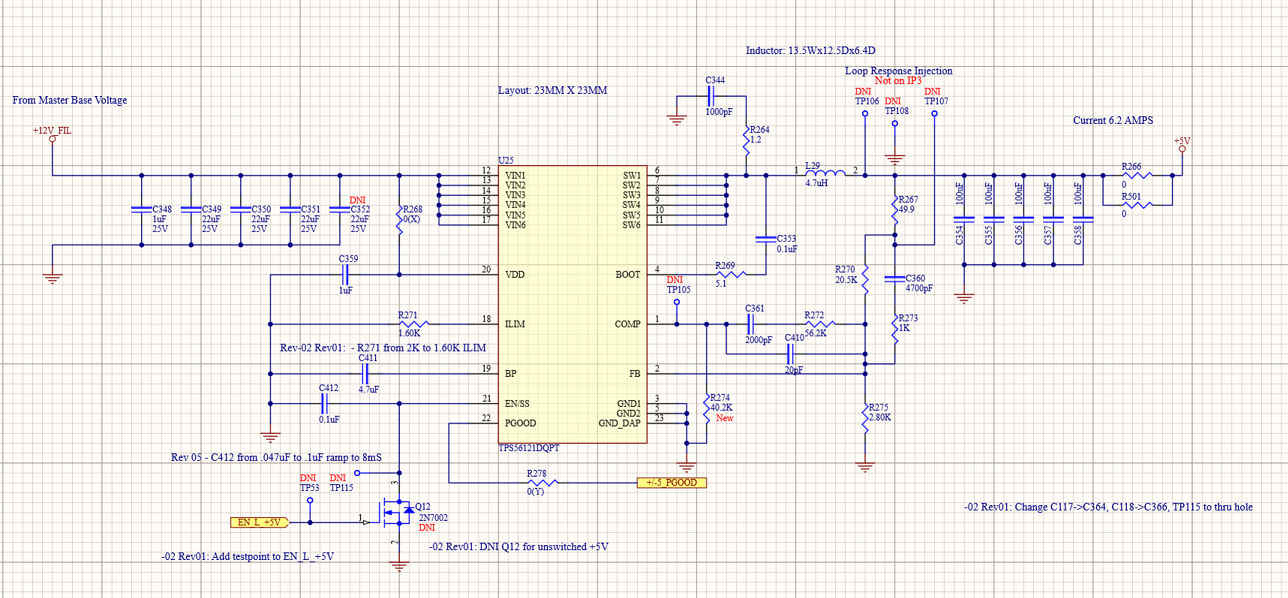

我们在设计中添加了电阻器和 FET 2N7002 N 沟道60V、以便实现受控启动和关闭。

当 FET 开关被启用时、+5V 电源不启动。

已检查器件值、温度和电流、似乎没有问题。

该单元在300kHz 下运行、但 在70kHz 下会有3AMPS 的大纹波电流、这可能是原因。

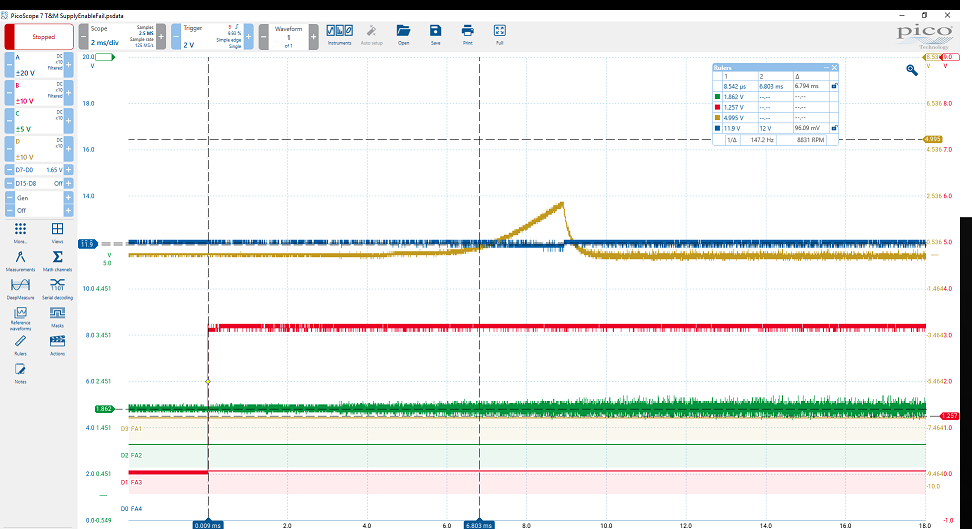

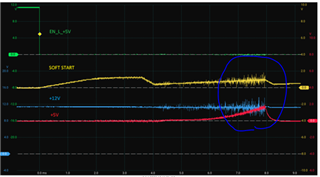

附加了电源使能(红色)、12V 电源(蓝色)、5V 输出(黄色)的 PICO 示波器捕获文件

+12V 线路上没有大压降表示存在大电流。

使能线看起来非常干净。

5V 电压开始上升但停止。 电源将尝试每50mS 重新启动一次、

是否存在可能导致此问题的其他内部故障情况?