大家好、TI 支持团队

我收到了客户的电路审查请求并正在进行询问。

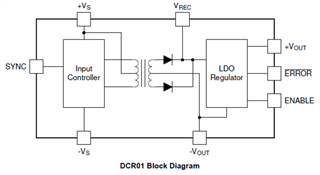

下面的图1是 DCR010505U 产品的电路图。

请检查是否有任何问题。

[主要考虑事项]

-电容器施加到 Vin 引脚: 47uF,低 ESR

-电容器施加到 Vout 引脚: 47uF,低 ESR

-电容器施加到 Vrec : 1uF,低 ESR

[图1]

图2是 Vrec 和-Vout 之间测量电压的图。

它实际上显示了6.8V 的差异。

这款器件不是问题吗?

(数据表中列出的整流输出(VREC)的典型值为5V。)

[图2]

通过相应的电路、通常输出 Vout、如图3所示。

[图3]

感谢您发送编修。

谢谢。

此致、

MJ