主题中讨论的其他器件:CSD18540Q5B

大家好、

据我们的客户称、Webench 建议的设计与实际的 PCB 设计并不一致。 他构建了 PCB 并测试了电路板。 请参看他的调查结果如下。

1.该器件在实际 PCB 中的效率下降了7%。 PCB 布局是在 Webench 中生成的设计。

2.如果输出电流为19A、Webench 推荐使用两个并联的 CSD18540Q5B MOSFET、但如果输出电流设置为20A、则建议仅使用一个 CSD18540Q5B MOSFET。

3.使用两个 MOSFET 时、器件的效率比单个 MOSFET 要低2%、并且都不符合 Webench 仿真中的效率

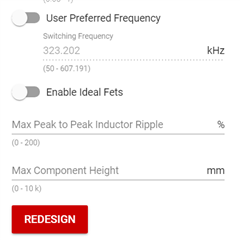

这是 WEBENCH 设计文件、

webench.ti.com/.../SDP.cgi

这些规格为:

输入电压= 30V

输出电压= 5V

IOUT = 20A

请参阅随附的客户 Excel 文件。

e2e.ti.com/.../0523.30V_5F00_to_5F00_5V_5F00_20A_5F00_BUCK.xlsx

这种错误可能是由什么原因引起的?

此致、

达尼洛