您好!

首先、感谢您更新了并行 LDO 的计算文件。

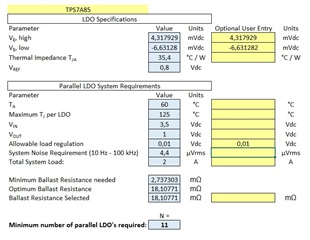

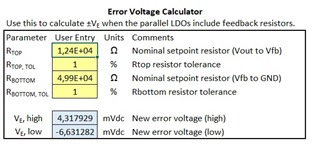

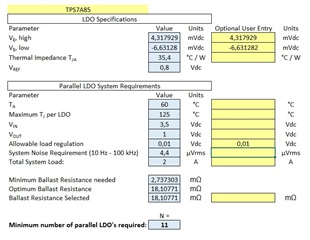

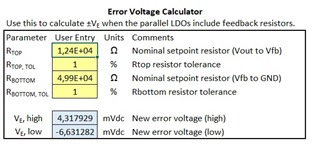

我尝试了最新版本、但使用相同的参数、与上一版本相比、计算存在很大差异。

请参阅链接: 上一篇有关 TPS7A85 (非 A) LDO 并行设计的文章

具体而言、计算得出的 Vₑ 高电平和 Vₑ 低电平与建议的最低 LDO 数量差别很大。

我是不是错过了什么?

提前感谢

安东尼奥·吉拉迪

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

首先、感谢您更新了并行 LDO 的计算文件。

我尝试了最新版本、但使用相同的参数、与上一版本相比、计算存在很大差异。

请参阅链接: 上一篇有关 TPS7A85 (非 A) LDO 并行设计的文章

具体而言、计算得出的 Vₑ 高电平和 Vₑ 低电平与建议的最低 LDO 数量差别很大。

我是不是错过了什么?

提前感谢

安东尼奥·吉拉迪

尊敬的 Antonio:

该计算器的最新更新仅在"error voltage calculer"选项卡上。 一位观察工程师注意到、为了获得此百分比、系统意外地将容差除以1000、而不是100。 在原始设计中、看起来我们假定电阻为1%、因此您可能希望切换到0.1%电阻。 请记住、这是最坏情况分析并且根据统计、您在生产中不太可能看到这种最坏情况解决方案。 虽然对于容差为1%的电阻器、所需的 LDO 最小数量增加了、但这是从最坏情况分析来看得出的、从统计角度来看、该数量应该更少。 您始终可以在 PSpice 中进行统计仿真、从而更真实地了解量产中的容差、具体请参阅本白皮书的第3部分:

https://www.ti.com/lit/wp/sbva100/sbva100.pdf

谢谢。

斯蒂芬