尊敬的团队:

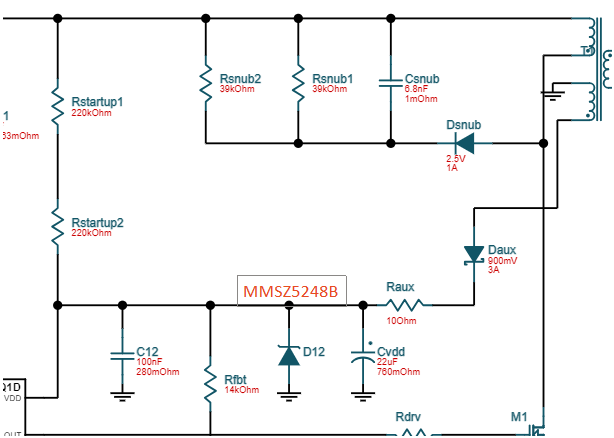

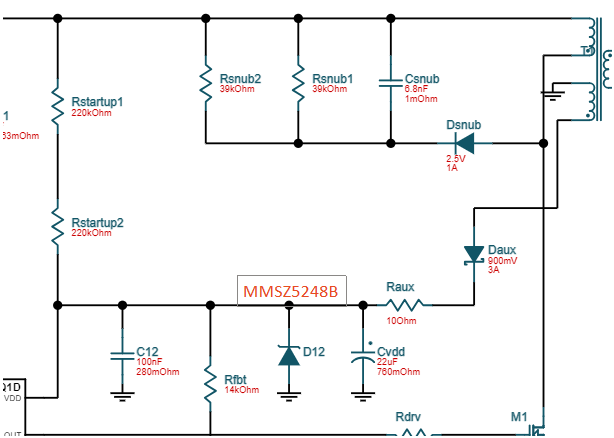

我正在设计输入电压为67至180rms 和输出电压为12V、电流为2A 的反激式器件。 我浏览了 Webench 原理图、发现连接在 VDD 引脚上的18V 齐纳二极管用于保护 IC。

D12为 VZ 18V @ IZT 7mA、现在有疑问、因为总 RVDd 为440K、 它允许0.21mA 为67V rms。 它应该允许7mA + 70uA 到 IC 开始 puls 正确吗? 0.21mA 有何帮助? 请解释

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的团队:

我正在设计输入电压为67至180rms 和输出电压为12V、电流为2A 的反激式器件。 我浏览了 Webench 原理图、发现连接在 VDD 引脚上的18V 齐纳二极管用于保护 IC。

D12为 VZ 18V @ IZT 7mA、现在有疑问、因为总 RVDd 为440K、 它允许0.21mA 为67V rms。 它应该允许7mA + 70uA 到 IC 开始 puls 正确吗? 0.21mA 有何帮助? 请解释

Manoj,

调整启动电阻的大小、使在最小输入电压下至少有75μA (所需的最小启动电流)可用。 Rstart=[67V*SQRT (2)-UVLO_ON]/nv= 75μA (94.75V-9V)/ 75μA = 1.1MΩ Ω。 您的设计显示440kΩ、这是195μA、这是所需的最低值的2.6倍、因此启动电阻器的大小正确。

当 VDD 超过 UVLO_ON 阈值时、开关开始、VDD 电平开始降低、直到 UVLO_OFF。 CVDD 电容器会保持 VDD 直至自举电压接管。 由于 VDD 仅达到 UVLO_ON、然后开始降低、直到自举绕组接管、因此在启动期间 D12不应导通。 调节主输出后、自举绕组将向主绕组进行交叉调节。 D12只会在瞬态或轻/无负载条件下进行 id VDD 尝试增加。 如果/当 D12导通时、这将发生在稳态运行期间、并且不会影响窃取启动 PWM 所需的启动电流。

此致、

史蒂夫