主题中讨论的其他器件:UCC21550

您好!

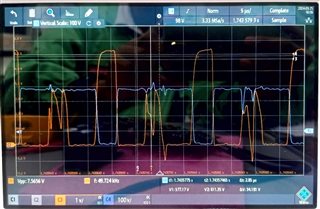

我将 UCC21520ADW 隔离式栅极驱动器 IC 用于图腾柱 PFC 交流/直流转换器。 问题在于在正半个周期内、开关 FET 的某些栅极脉冲不完整、并且在某些时间段内无法完全形成输出脉冲。 这个问题是随机发生的。 我还检查了栅极驱动器 IC 的输入信号、并在此处附上了图像以供参考。

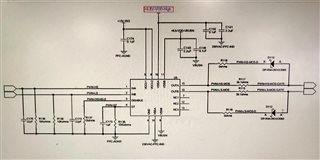

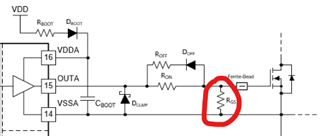

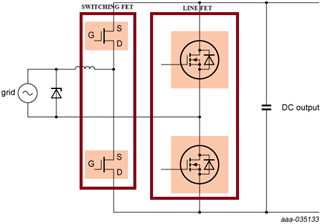

我的电路:

橙色波形- PFC 高电平 FET 的栅极驱动器输入信号

蓝色波形- PFC 低电平 FET 的栅极驱动器输入信号

此处连接了从驱动器 IC 观察到的输入信号输出栅极脉冲、供您参考。

蓝色波形 -低 FET 漏极

橙色波形-驱动器 IC 输出端的低 FET 栅极脉冲

请就上述问题提供您的建议。

谢谢。

Vignesh。