主题中讨论的其他器件:TINA-TI、 UCC21550

您好!

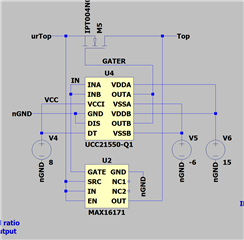

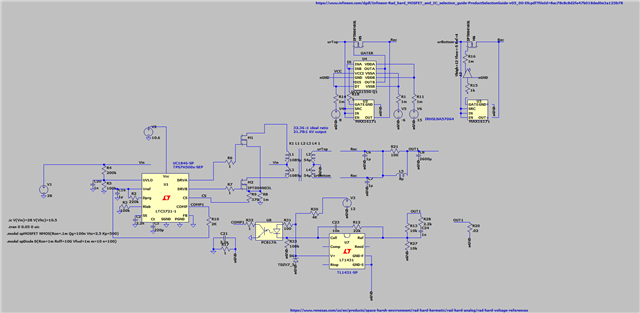

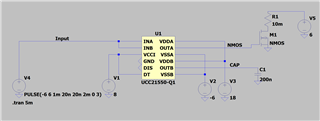

我下载了 UCC21225A PSpice 瞬态模型 、并使用此处所述的方法将其转换为 LTSpice 模型: https://www.onethesis.com/how-to-create-an-ltspice-model-from-pspice-or-tina-ti-model/

虽然这种方法适用于其他器件、但我在此器件方面存在问题。 首先、 每当我停止仿真时、我都会收到一组错误(请参阅底部的错误)

其次、在将器件添加到现有设计中时、有时会导致仿真更改输出、即使它未连接到任何对象也是如此。

在其他仿真中(每次仿真中出现的错误似乎是随机的)、仿真将运行几个时间步长、然后仿真将冻结。

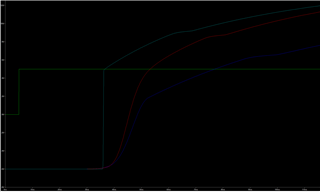

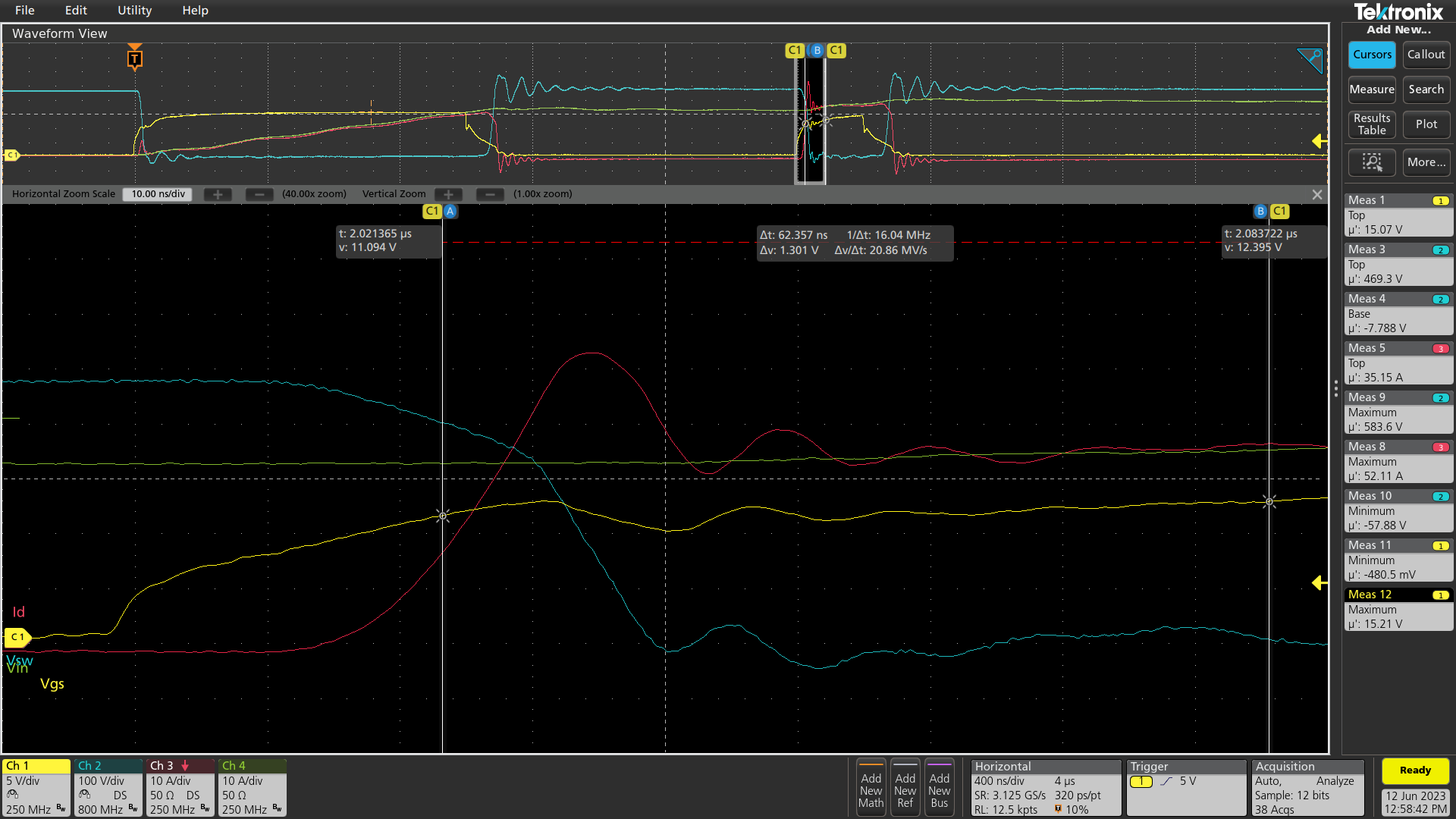

最后、在极少数情况下、它可以正常工作、因此输出看起来很奇怪。 输出(OUTA/OUTB 当连接到 FET 时)将立即以2个时间阶跃(~2ps)增加9V、然后需要~100ns 时间才能在看起来像电容器充电的曲线之后上升最后几伏。

我确信所有这些问题都是关联的、模型有问题、很遗憾、我不知道问题是出在 PSpice 模型还是我的转换中、或者是我做的其他一些假设。

非常感谢您提供任何信息!

错误:

关于"b§e_abmgate yint 0 v={if (v (a)>{vTHRESH}&v (b)>{vTHRESH}、{VDD}、{VSS}}"中使用花括号的问题

错误:未定义的符号位于:"if ([v](a)>(vthresh)&v (b)>(vthresh)、(VDD)、(VSS)"

关于"b§e_abmgate yint 0 v={if (v (a)>{{vthresh}}、{{VSS}}、{{VDD}})}中使用花括号的问题

错误:未定义的符号位于:"if ([v](a)>((vthresh))、((VSS))、((VDD))"

关于"b§e_abmgate yint 0 v={if (v (a)>{vTHRESH}&v (b)>{vTHRESH}、{VDD}、{VSS}}"中使用花括号的问题

错误:未定义的符号位于:"if ([v](a)>(vthresh)&v (b)>(vthresh)、(VDD)、(VSS)"

关于"b§e_abmgate yint 0 v={if (v (a)>{{vthresh}}、{{VSS}}、{{VDD}})}中使用花括号的问题

错误:未定义的符号位于:"if ([v](a)>((vthresh))、((VSS))、((VDD))"

关于"b§e_abmgate yint 0 v={if (v (a)>{vTHRESH}&v (b)>{vTHRESH}、{VDD}、{VSS}}"中使用花括号的问题

错误:未定义的符号位于:"if ([v](a)>(vthresh)&v (b)>(vthresh)、(VDD)、(VSS)"

关于"b§e_abmgate yint 0 v={if (v (a)>{{vthresh}}、{{VSS}}、{{VDD}})}中使用花括号的问题

错误:未定义的符号位于:"if ([v](a)>((vthresh))、((VSS))、((VDD))"

关于"b§e_abmgate yint 0 v={if (v (a)>{vTHRESH}&v (b)>{vTHRESH}、{VDD}、{VSS}}"中使用花括号的问题

错误:未定义的符号位于:"if ([v](a)>(vthresh)&v (b)>(vthresh)、(VDD)、(VSS)"

关于"b§e_abmgate yint 0 v={if (v (a)>{{vthresh}}、{{VSS}}、{{VDD}})}中使用花括号的问题

错误:未定义的符号位于:"if ([v](a)>((vthresh))、((VSS))、((VDD))"

关于"b§e_abmgate yint 0 v={if (v (a)>{vTHRESH}&v (b)>{vTHRESH}、{VDD}、{VSS}}"中使用花括号的问题

错误:未定义的符号位于:"if ([v](a)>(vthresh)&v (b)>(vthresh)、(VDD)、(VSS)"

关于"b§e_abmgate yint 0 v={if (v (a)>{{vthresh}}、{{VSS}}、{{VDD}})}中使用花括号的问题

错误:未定义的符号位于:"if ([v](a)>((vthresh))、((VSS))、((VDD))"

关于"b§e_abmgate yint 0 v={if (v (a)>{vTHRESH}&v (b)>{vTHRESH}、{VDD}、{VSS}}"中使用花括号的问题

错误:未定义的符号位于:"if ([v](a)>(vthresh)&v (b)>(vthresh)、(VDD)、(VSS)"

关于"b§e_abmgate yint 0 v={if (v (a)>{{vthresh}}、{{VSS}}、{{VDD}})}中使用花括号的问题

错误:未定义的符号位于:"if ([v](a)>((vthresh))、((VSS))、((VDD))"

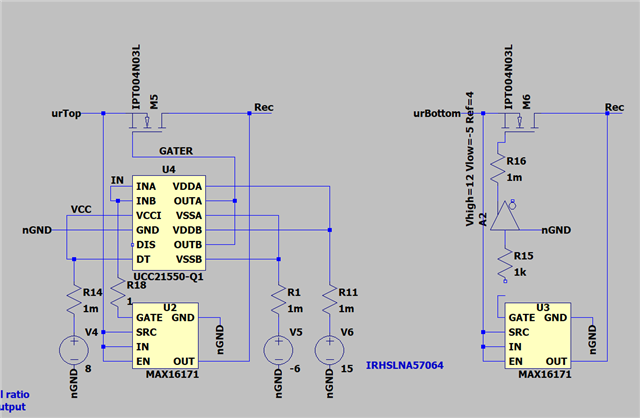

绿色线是 INA 的输入、蓝色线是输出 OUTA。 经过19ns 的传播延迟后、在转换到更"正常"的充电曲线之前、输出以看似不可能的速度从-6V 跃升至刚刚超过3V。