Other Parts Discussed in Thread: UCC27712

您好!

我使用两个 ucc27712来构建一个全 H 桥。 我今天测试了电路、发现了一些问题。

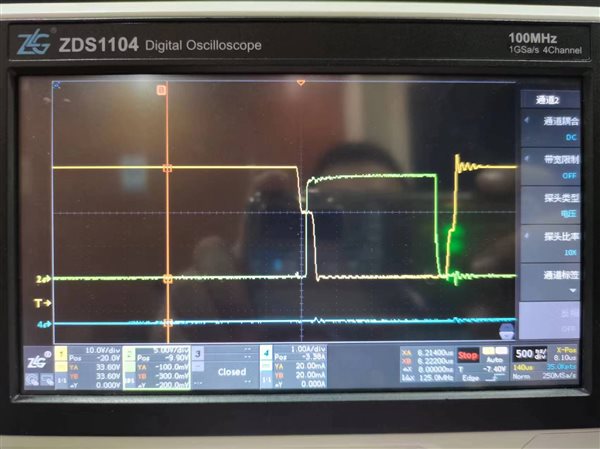

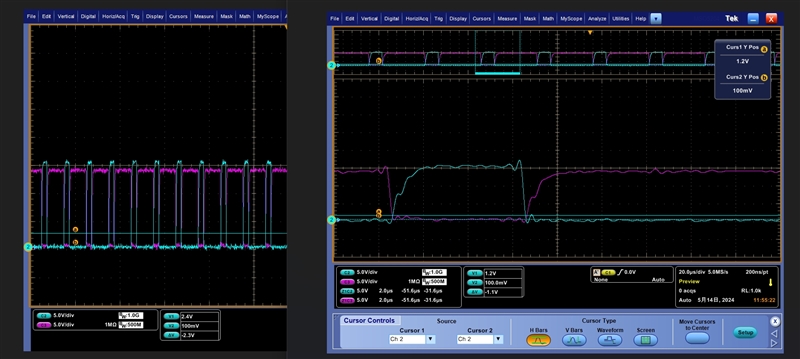

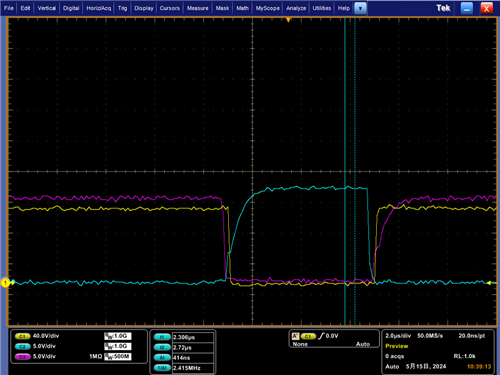

我首先发现当我 断开负载时 MOSFET 变热、然后测试了 Ucc27712、HO 和 LO 的输出如下

我无法理解输出下降时的阶跃、我想正是这一原因导致上下 MOS 同时导通、使得它们变热。

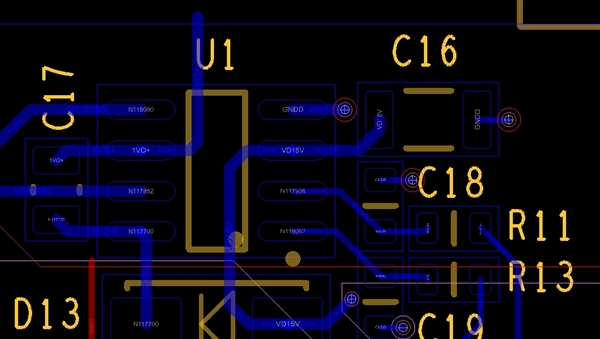

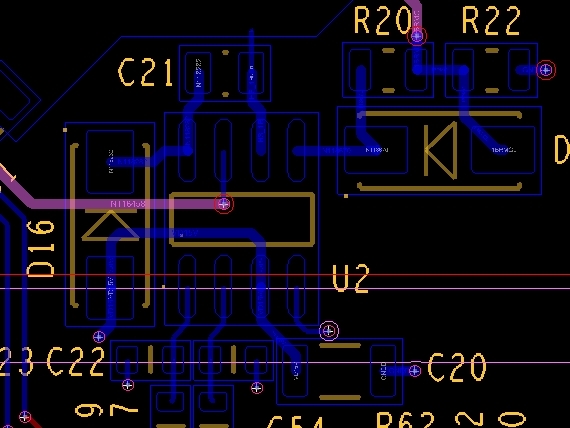

我的原理图如下。MOS 的器件型号为 IPP410N30

我还测试了74HC4049的延迟、该值约为8ns。

请帮我

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Other Parts Discussed in Thread: UCC27712

您好!

我使用两个 ucc27712来构建一个全 H 桥。 我今天测试了电路、发现了一些问题。

我首先发现当我 断开负载时 MOSFET 变热、然后测试了 Ucc27712、HO 和 LO 的输出如下

我无法理解输出下降时的阶跃、我想正是这一原因导致上下 MOS 同时导通、使得它们变热。

我的原理图如下。MOS 的器件型号为 IPP410N30

我还测试了74HC4049的延迟、该值约为8ns。

请帮我

嗨、

感谢您就有关 UCC27712的问题与 TI 取得联系。

我有几个问题可以帮助我更好地了解您的情况。

1.您是否通过差分探头测量相对于 HS 的 HO? 通过电平转换使高侧以 HS 为基准、因此高侧 FET 的 Vgs 为 HO-HS。 如果您没有差分探头、则可以测量 HS-HS VSS 和 HO-HS VSS、并使用示波器上的数学通道来确定 HO-HS。

C16和 C20是否靠近栅极驱动器放置? 它们需要能够拉电流以实现高负载瞬态。 另外、这些应该是 X7R 陶瓷电容器、值47uF 远高于预期。 对于0.1uF 自举电容器、我们建议使用比自举电容器 C16和 C20 X7R 大10倍的旁路电容器。

3. HI 和 LI 输入信号之间的死区时间是多少?

如果您有任何问题、请告诉我。

谢谢!

威廉·摩尔

您好!

感谢您的答复。

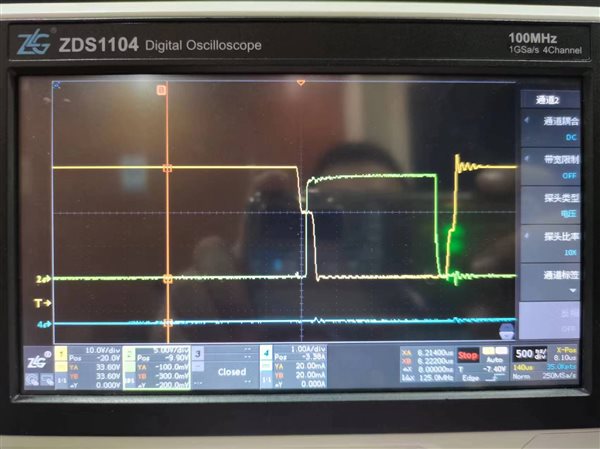

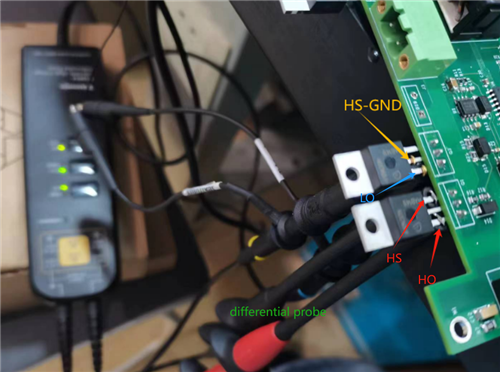

1我试过一些条件,我用 I 差分探头测量 HO-Hs(紫线),用普通探头测量 LO-Hs( VSS 蓝线)

A IPP410 NMOS,40kHz PWM、C16&C20=47uF、VD96=30V、波形如下

b vd96v=96V

有太多杂散,但我不知道为什么

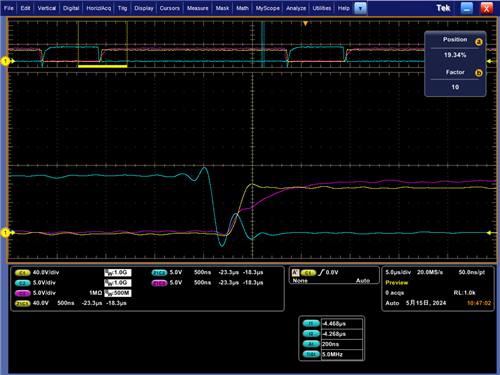

C I 将 C16&C20值更改为1uF

d 我发现了一个早于 zhe IPP410的电路板、mos 器件型号为 IRFB4127 (IPP410晚于 IRFB4127交付),唯一的区别是 NMOS

4127+1uf (C16和 C20)+40kHz+96V、波形遵循

在测试过程中,我发现 mos 在1个月内变热,温度上升超过40度。mos irfb4127较低,但也变热。

2我的布局如下

3我仅使用一个 PWM 信号作为高 PWM、并使用反相栅极生成低 PWM。

我的问题:

1我无法理解为什么两个 MOS 导致波形的差异

2 我想知道我应该怎么做来解决这个杂散和热莫斯的问题

非常感谢

嗨、

您是否可以采集包含 HO-HS、LO-HS VSS 和 VSS 的波形?

在此测试期间、HS 开关节点的状态是什么? 它是否悬空?

HS 似乎在 LO 上升沿期间仍然为高电平、并导致体二极管导通、直到 LO 变为高电平并可以将 HS 拉至低电平。 这将产生大量开关损耗、从而可能导致产生热量。

对于 LO 上升沿的过冲、您可以通过 IPP410N30N 看到这一点。 这可能是由较低的栅极电荷和较大的米勒电荷差异造成的。

您在何处以及如何进行测量? 它们是否使用尖头与桶形探针来连接栅极驱动器的引脚?

如果您有任何问题、请告诉我。

谢谢!

威廉·摩尔

您好!

我的 HS 悬空、因为我没有客户要求的负载。

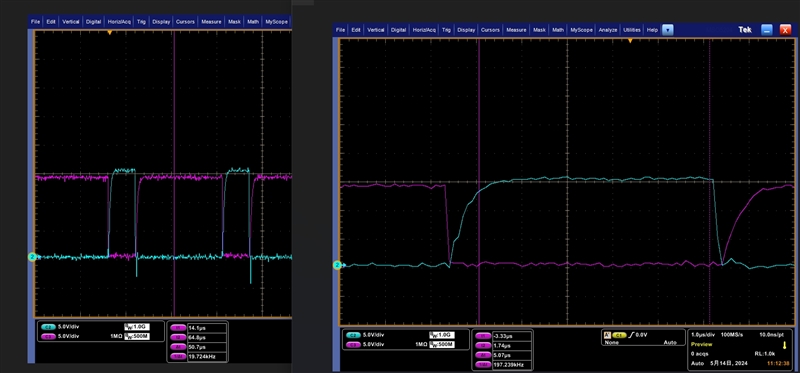

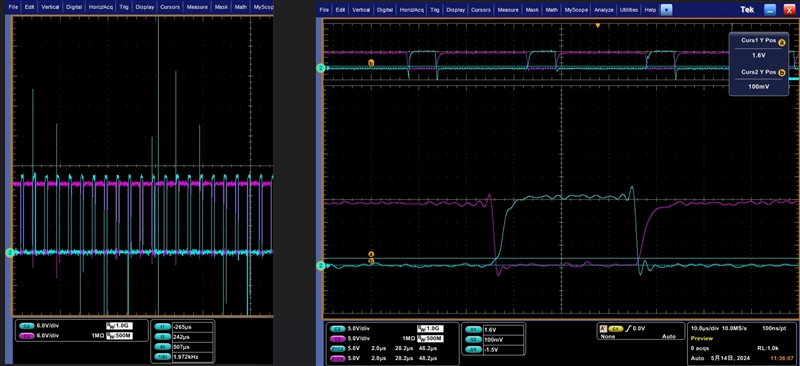

我重复测试拍了这些照片:黄线是 HS-HS VSS,紫线是 HO-HS,蓝线是 LO VSS:测试板是用 irfb4127

当我用另一个板进行测试时、我发现 LO 信号的波形不同、该信号在下降沿后上升

1我想你是对的, HS 在低上升沿期间仍然有效。 如何解决此问题?

2如何减少下降沿后的 LO 上升?如果我将 ipp410n30替换为另一个可以正常工作的 NMOS? (IRFB4127 VDS 中断为200V、与我的需求不符)

谢谢!

嗨、

HS 在 LO 上升沿期间仍然为高电平的原因是开关节点(HS)悬空、因此无需将其下拉至接地、而如果在空载条件下有输出级连接到它、 它能够将 HS 引脚接地。

2.要调整上升/下降沿的 dV/dt,可通过改变栅极电阻来实现。 但是、您在下降沿之后看到的 LO 上的这个额外上升沿可能是由于另一个半桥的米勒电荷导致了这个错误脉冲、此时出现了高 dV/dt 上升沿。 较低的栅极电荷(Qg) FET 将具有更快的导通上升沿。

您是否在连接输出级且 HS 未悬空的空载条件下尝试过此方法?

当还有负载时、您是否也会遇到此问题?

您看到的情况可能是由于 MOSFET 寄生效应、而不是栅极驱动器操作、因为栅极驱动器似乎按预期运行。

如果有任何问题、请告诉我。

谢谢!

威廉·摩尔

嗨、

在负载条件下、下冲似乎不会导致正常的上升沿、这种情况仅发生在 IPP410N30N 中。

此 MOSFET 具有更低的 Qg、因此上升沿和下降沿的压摆速度将比 IRFB4127快。

为了减少 LO 上的这种下冲、您可以增加关断路径通过关断二极管的栅极电阻。 此外、您还可以添加钳位肖特基二极管、以帮助限制这种下冲。

导致我先前提到的错误脉冲的另一个半桥的米勒电荷在这里仍然有意义。

如果您有任何问题、请告诉我。

谢谢!

威廉·摩尔