尊敬的 TI 专家

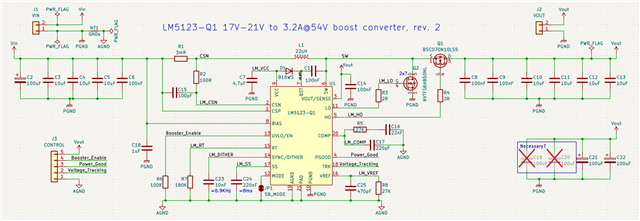

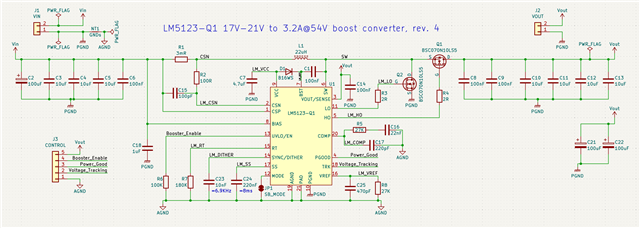

请您查看此升压转换器设计的组件选择和布局。

背景说明:这是一个通过5S2P 锂离子电池组供电的 LED 驱动器。 (电流)调节通过具有外部 MCU 和电流感应电阻器的跟踪输入完成。 还有一个外部低侧开关、用于快速开启或关闭 LED (选通功能)。

转换器用于 在 17.5V 最小输入下在3.2A@54V 的全功率输出下正常工作。

为了最大限度地降低这种热挑战应用中的开关损耗(附近的冷却风扇仅有少量气流)、选择了大约120kHz 的相对较低的开关频率。

否则、电感器会很大、昂贵且可用性差、因此必须选择大约60%的高纹波电流比。 我接受由此产生的更高内芯损耗和更低轻负载效率(较早的 DCM)。

PCB 是一个6层板、具有镀层填充过孔和1-0.5-0.5-0.5-1盎司的覆铜厚度。 使用6层是因为应用的其他部分都需要它们。

我关注的主要问题是:

- 您是否建议使用小于快速入门计算器建议值的电流感应电阻器值? 正如我所看到的、它将减少损耗和低频增益。 电流限制也会过高、但电池保护电路已经解决了这一问题。 2mΩ 甚至1mΩ 也可以吗?

- QH-QL-COUT 环路足够小吗? 是否需要更多小输出电容器? 目前在 QH 旁边有两个0805 100nF X7R 输出电容器、在器件附近有一个。

- RS-LM-CIN 环路不那么重要(di/dt 更小)、但也没有问题吗?

- 直接连接 SW/HO/VOUT 是否足够? "附件"电容器有点麻烦、但我不想使用具有较差直流偏置特性的较小封装。

- LO/GNDPWR 直接连接是否足够? LO 很宽、在 GNDPWR 平面上运行、但中间有过孔。

- 我包围了相当长的电流检测轨迹、其中上方和下方具有 GNDA 区域。 这是一个不好的主意吗?

- SW 覆铜位于较小的一侧。 我认为电感器的大块铜线会吸收部分热量、因此不需要有一个大噪声平面进行散热。

编辑:已从此问题中删除所有附件、因为它们被报告为缺失!

提前感谢您、

艾达里安