我正在设计 USB 5V 供电的单节锂聚合物电池充电电路。 我们要在3.0 - 3.3V 逻辑电平微控制器中设置 I2C 通信和中断、以监控 BQ25628E 寄存器。 我知道、在典型应用电路中、VREF 是主机 MCU 的逻辑电压、尽管数据表中似乎没有明确说明这一点。

1.请您确认 VREF 的用途是什么?

此外、我们寻求实现最低功耗电路、从而使主机 MCU 进入睡眠模式。 我们计划使用10k 电阻器为 MCU 上的 GPIO 上的 I2C SDA/SCL 和 BQ25628E INT 上拉电阻供电、以便可以关断上拉电源轨以实现最低功耗运行。

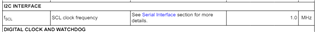

2.您能否详细说明 I2C 和 INT 上拉电阻在使用10k 欧姆电阻器和3.3V (数据表给出了1.8V 的值)的情况下应汲取多少泄漏电流、并建议最佳方案来降低 BQ25628E 周围/周围支持电路中的泄漏/静态电流?

3.在 MCU 的低功耗模式下、我们最好不要将 I2C 和/或 INT 线路拉高、以便更大限度地降低泄漏电流、还是在 MCU 睡眠时将它们拉至接地?