主题中讨论的其他器件: UCC28950

尊敬的 Mike O'/团队:

我想开始测试组装在 PCB 上的控制器(UCC28951)。 我正在准备一个测试计划开始测试。 请提供导游。

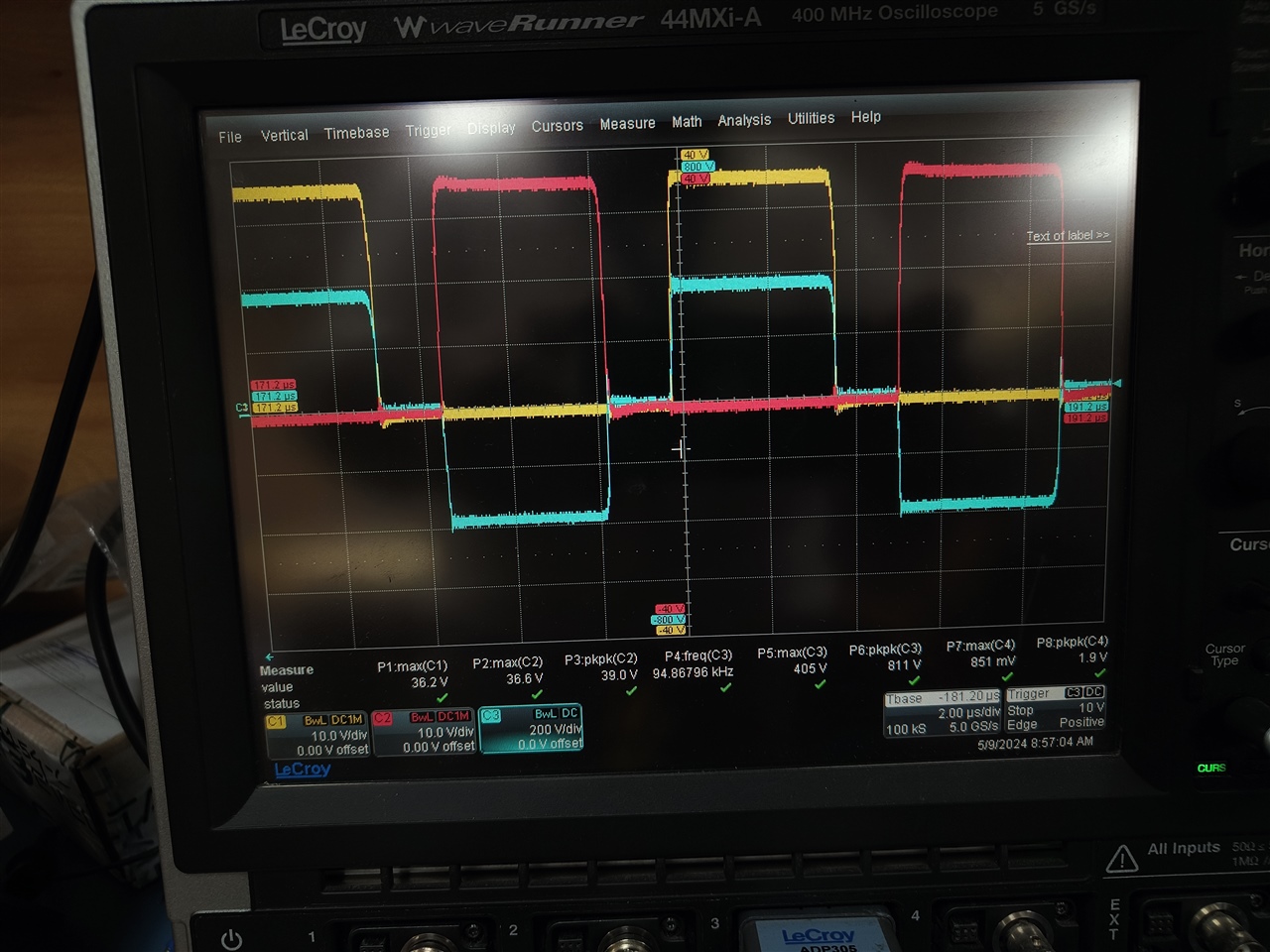

我想在空载条件下启动、然后按照线性顺序缓慢提供负载电流。

我的最大负载电流大约为80A。 最小值为2A。

TMIN 电阻:13k. 我是否应该进一步降低 Tmin 电阻值、或者这是正确的?

在数据表第7.3.9节(突发模式)中、显示了 如果控制器仍要求占空比小于 TMIN、则控制器会进入关断模式。

我会对不同的运行模式感到困惑。 根据我的理解、当释放 SS/EN 引脚之后控制器启动时、应该在空载条件下调节输出电压。

然后、假设我提供2A 的负载电流(这将是非常轻的负载条件)、

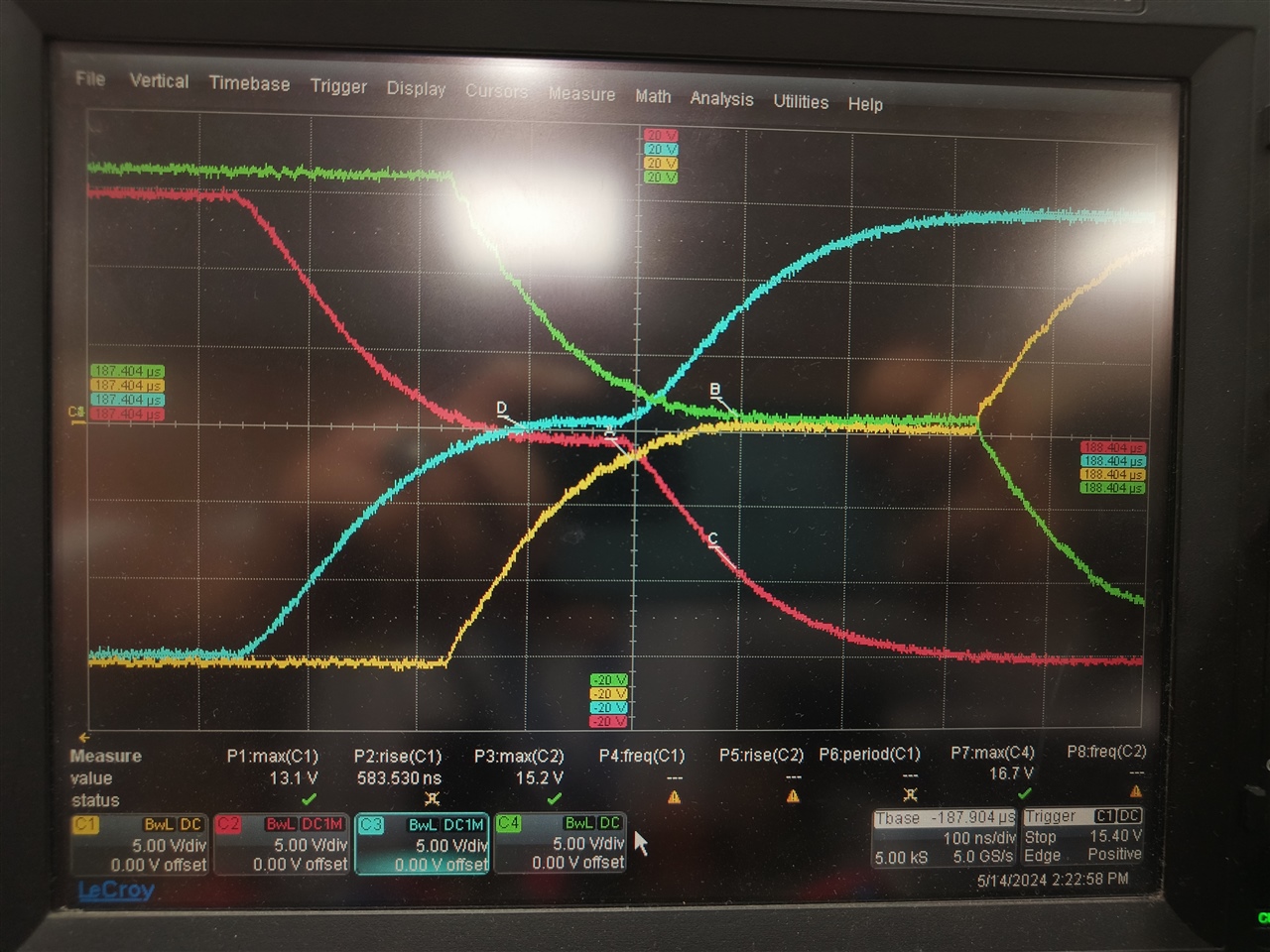

然后、假设我将负载电流增加到5A、它将进入 DCM 模式还是仍处于突发模式?

进一步增加(在本例中约为10A)负载电流的15%以下、这是巨大的、因为 FET 二极管会变热、它将保持在 DCM 模式下。 对吧?

负载电流超过15%时、控制器进入 CCM 模式。 我想了解我对操作的理解是否是电流的理解、以及在测试时可能需要做哪些调整/值变化? 请指南。

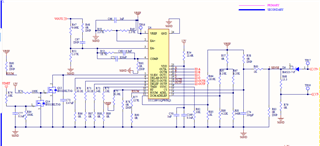

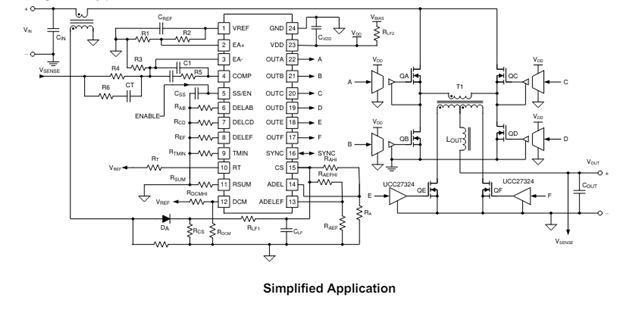

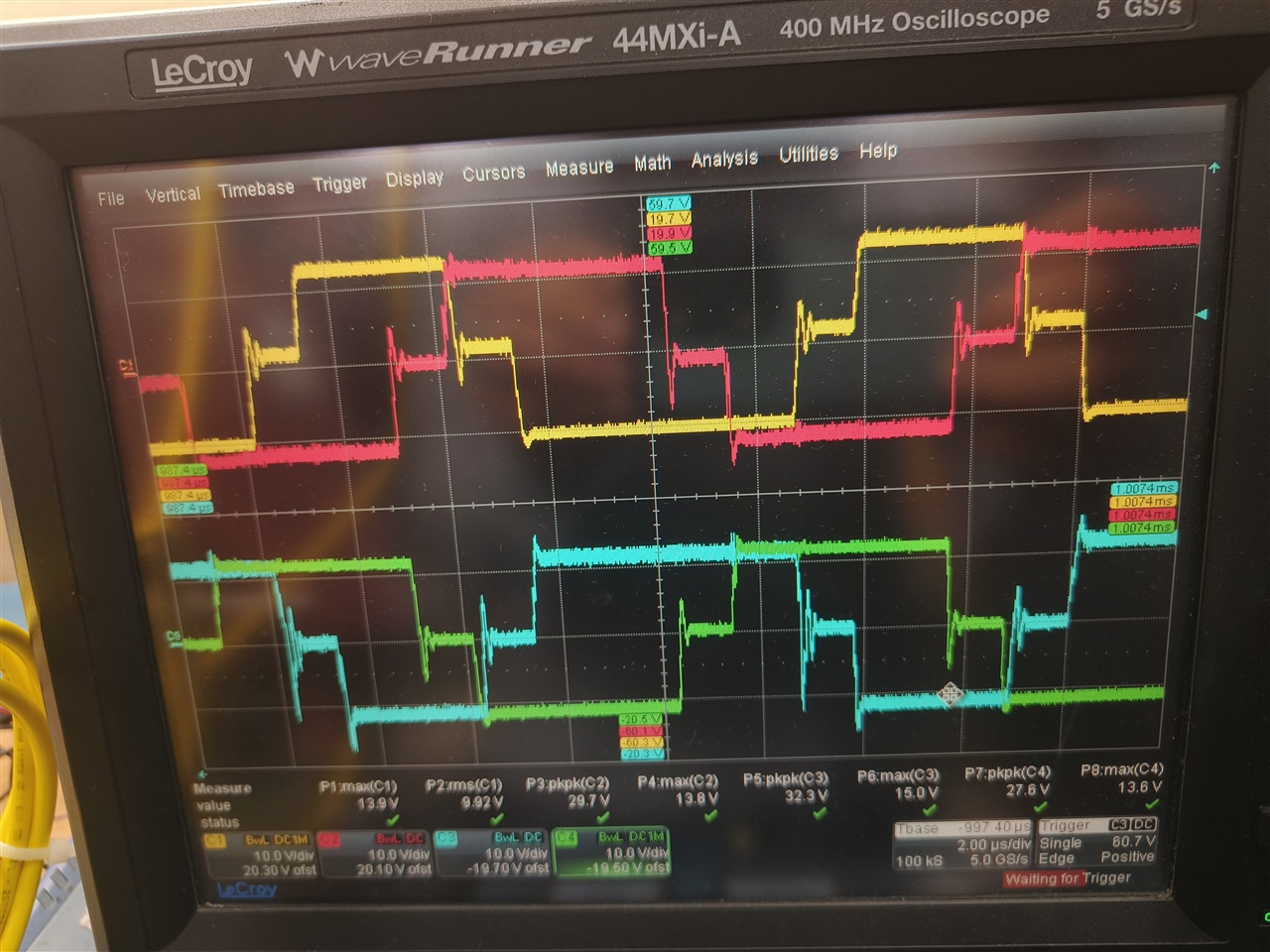

找到下面的电路图。