主题中讨论的其他器件:TPS3851

工具与软件:

您好、TI 专家

我的问题如下所示。

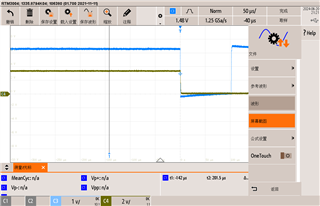

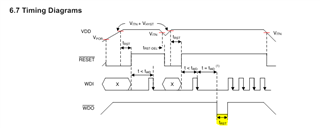

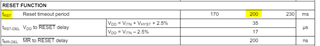

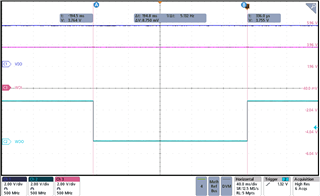

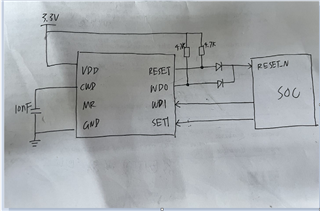

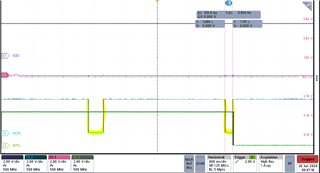

如图(蓝色 曲线)所示、我们产品使用的 WDO tRST 大约只有100us、WDO 管脚与我们公司的 SOC 相连。 但在另一个测试中、 当 WDO 引脚连接到 Xilinx 产生的 FPGA 时、WDO tRST 大约为2ms。 因此、我想知道 WDO tRST 是否 由负载(SOC 系统)决定。 数据表中显示的典型 WDO tRST 就是芯片可以支持的最大复位超时周期? 我不知道 WDO tRST 是否 合理、因为它与数据表不同。 谢谢!