工具与软件:

您好!

当我使用 UCC27714驱动 H 桥时、 击穿通常出现。Ω

我想。电路设计中是否存在任何不合理的情况

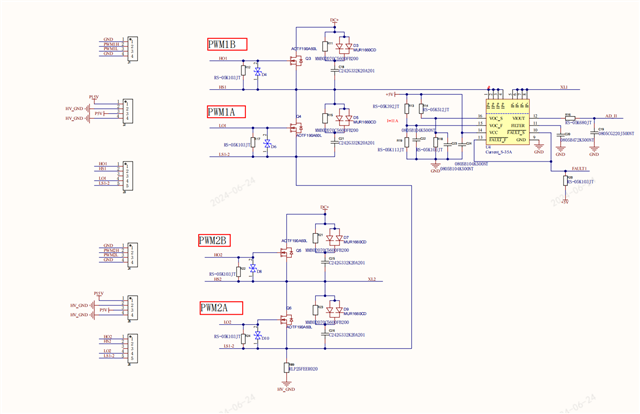

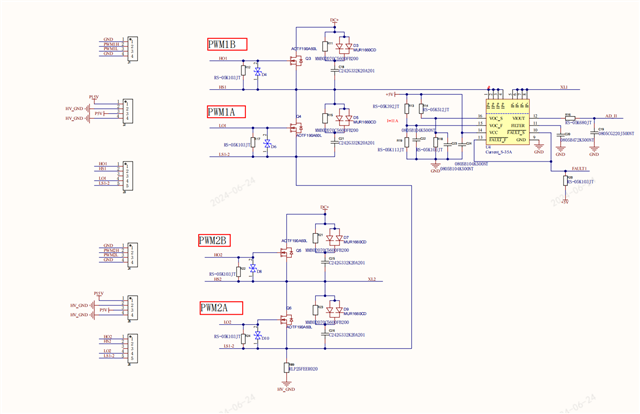

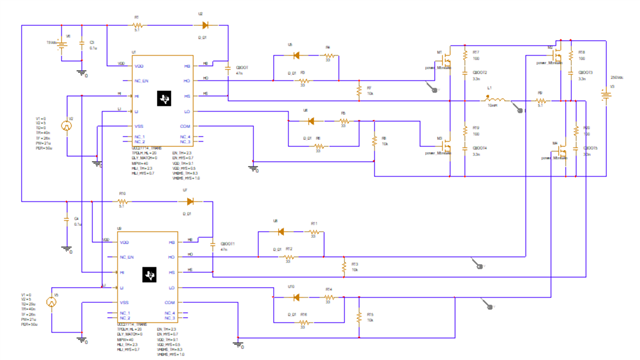

图1:H Brigde、电流传感器、我的负载在 XL1/XL2之间具有10mH 电感

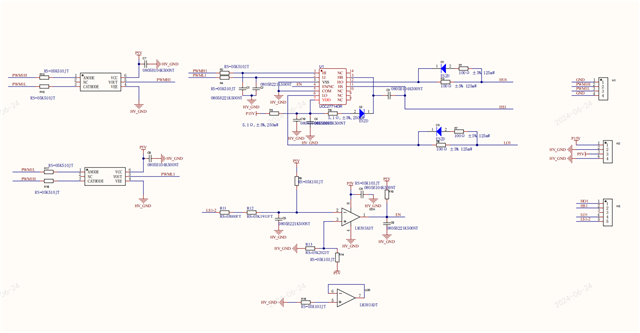

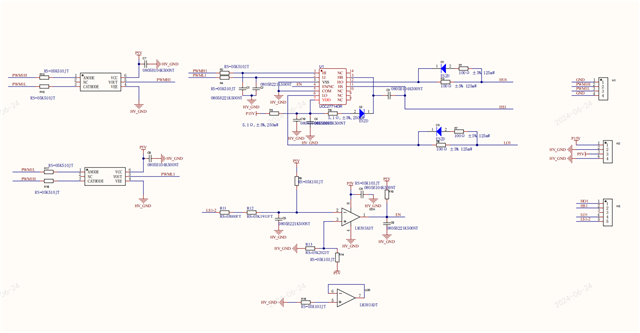

图2: 驱动电路

图3:我的测试波形、DEADTIME=4us。

CH1、CH2:PWM1A、PWM2A

Ch3、Ch4:PWM2A、PWM2B

;

;

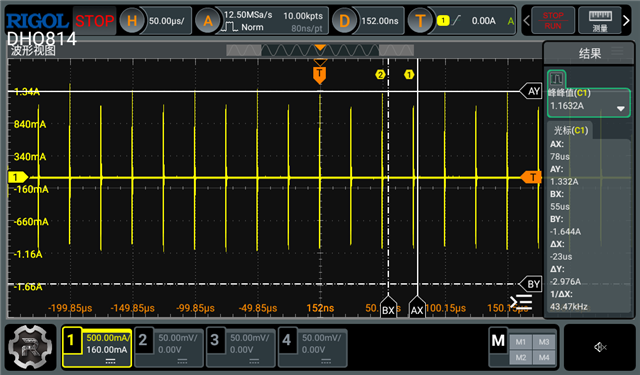

图4:这是我正确运行时的电流波形、另一个问题是我需要进行哪些调整来减少这些电流脉冲

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好!

当我使用 UCC27714驱动 H 桥时、 击穿通常出现。Ω

我想。电路设计中是否存在任何不合理的情况

图1:H Brigde、电流传感器、我的负载在 XL1/XL2之间具有10mH 电感

图2: 驱动电路

图3:我的测试波形、DEADTIME=4us。

CH1、CH2:PWM1A、PWM2A

Ch3、Ch4:PWM2A、PWM2B

;

;

图4:这是我正确运行时的电流波形、另一个问题是我需要进行哪些调整来减少这些电流脉冲

嗨、

感谢您就您有关 UCC27714的问题联系 TI。 我有几个问题可以帮助您更好地了解您的设置和问题。

1.是否同时开启每个半桥中的两个 FET? 在您共享的第一个波形中、PWM2A 和 PWM2B 同时为高电平、这看起来是这样的。 如果是这种情况、您将看到击穿、因为在这种情况下、直流母线将通过此半桥直接接地。

2.可以放大输出电流波形上看到的电流峰值以便看到其中的1个或2个吗?

3.能否分享栅极驱动器的原理图以及列出的所有元件值?

4.自举二极管的电阻 R6大于预期值、可能降至1欧姆或2欧姆。 这会减慢自举电容器的充电时间。

5.栅极电阻值100欧姆大于预期值。 这可以缩短上升和下降时间、但也可以减少过冲。 2-15欧姆范围内的电阻器更接近预期值。 此外、在关断路径中使用相同尺寸的电阻器将导致不使用关断路径、因为由于二极管的电阻、该电阻会更高。 关断路径中的此电阻器应比栅极电阻器小得多。

如有任何问题、请告诉我。

谢谢!

William Moore

您好、William Moore:

1、同时打开下侧的 MOS ,然后打开高侧的 MOS ,为零三级

2.放大电流峰值、 开关周期为20kHz、PWM1B、PWM2A 相移180度关系、PWM1A、PWM2B 也是如此。

电流尖峰似乎在开关时出现。

3.i 在实际电路做了一些修改、简化的原理图如下:

4.感谢您的建议。 我来试一下

5.您是对的。 我已经将电阻调整到10欧姆

此致、

您好、 William Moore:

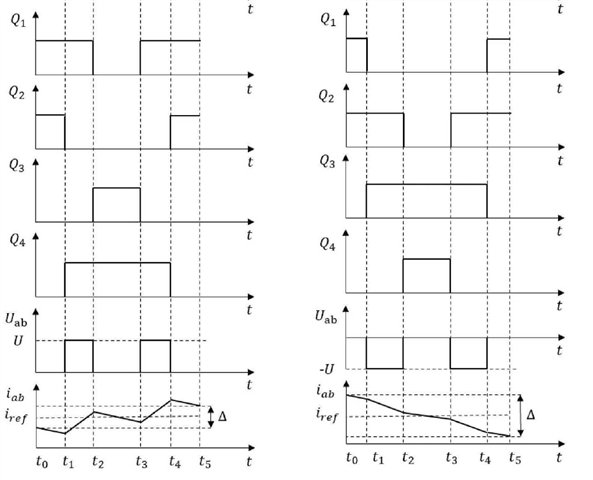

这样做可以使电感器电流在单个控制周期内保持恒定、如下所示:

Q1和 Q3 是 左半桥的高侧和低侧

Q2和 Q4是 右半桥的高侧和低侧

IAB 是电感电流。 我的驱动波形对应于图中的 T2-T3。

另一个让我感到困惑的问题是、当我使用该波形测试电路时、对于不同的负载电感器、结果是不一致的。

我的负载变化约为10mH±5%、有些效果很好、但有些会发生 击穿

当我调整 RC 缓冲器电路、它甚至损坏我的驱动电路。

我想知道设计是否有任何问题。

此致、

嗨、

您之前展示的电流尖峰波形在这种情况下似乎会发生击穿。

看看您在初始帖子中发送的波形和您最近共享的原理图、您似乎在以大约50%的占空比同时打开 M1和 M2、而 M3和 M4似乎相反。 这是因为 LI (U1)和 LI (U2)连接在一起以及 HI (U1)和 HI (U2)连接在一起。

为了完成上述时序图、您需要4个独立的 PWM 信号来控制4个单独的 FET。

此外、请确保上升沿和下降沿之间有足够的死区时间、以防止潜在的击穿情况。

如有任何问题、请告诉我。

谢谢!

William Moore