工具与软件:

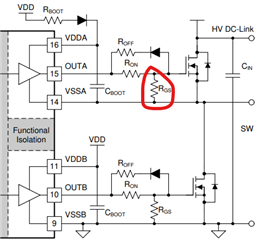

每个 UCC21222D 芯片均驱动由 P 沟道(高侧)和 N 沟道(低侧) MOSFET 组成的半桥。 遗憾的是、由于逻辑中的问题、有时我们会在两个输入上同时得到正脉冲。 我们正在努力寻找并解决这个问题、但在此期间、我们最后希望防止击穿的 是芯片的这一特性、以防止同时输出和死区时间设置。 死区时间通过100kOhm 电阻设置为~ 1uS。 我们的两个输出通道都由相同的12V 电源供电、通过两个电容器0.1uF 和4.7uF 旁路。 该12V 输出驱动源可能存在短暂的压降、但示波器尚未发现这种压降。

然而、当输入有源脉冲同时到达时、MOSFET 正被烧毁。 什么地方出错了? 为什么芯片不阻止同步输出? 此驱动芯片上是否有勘误表?

请提供帮助。