主题中讨论的其他器件:TPS650861、、 TPS65086

工具与软件:

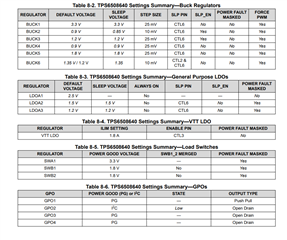

我使用 TPS6508640器件设计电源模块。 针对此系列稳压器、其反馈引脚通常连接到开关电感器的输出端。 在另一个论坛项目中、询问了如何补偿由于负载迹线而导致的压降。 答案是输出电感应放置在靠近负载的位置。 但在本例中、无法实现这一点、因为设计位于远离负载的单独模块中。

问题如下:

反馈是否应该仍然连接到电感器的输出或者是否应该输出模块上的反馈引脚、以便它能够被连接到主板上的实际负载?

非常感谢

Michael Stamler