主题中讨论的其他器件:CSD18563Q5A、 LM5146、LM5145

工具与软件:

嗨、团队:

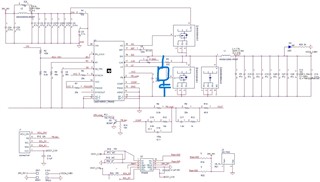

我曾在 e2e 上提出过如下有关原理图和布局设计的问题:

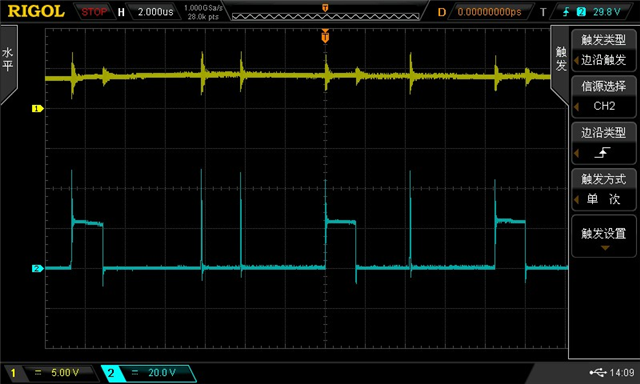

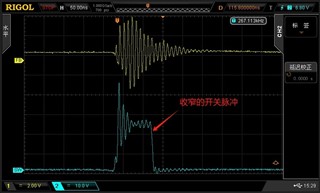

但现在客户根据我们的建议并修改了原理图、发现每个周期的占空比不同、如下所示:

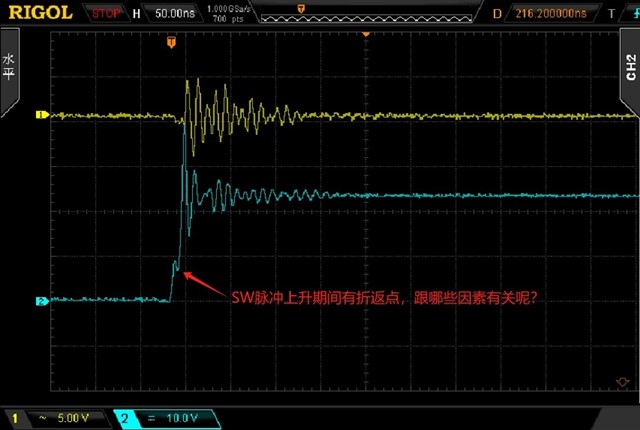

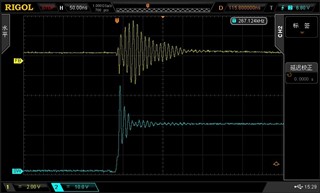

此外、开关瞬间过脉冲的嘎嘎声非常严重、导致输出噪音很大

宽占空比

窄负荷

黄色为 FB 引脚、蓝色为 SW 引脚。 从上面的图片中、我想 振铃也是导致占空比的原因。 并形成输出、便可以获得稳定的输出电压。 振铃可能是主要问题。 您能帮忙检查一下吗、告诉我们如何解决振铃问题?