工具与软件:

嗨、团队:

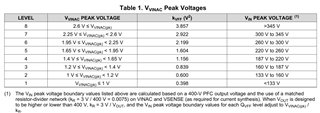

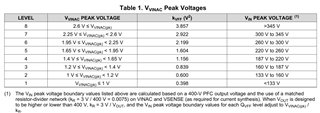

当使用 AC170~264V、750Vout 进行设计时、根据表1中的注释、kr = 3V/750V = 0.0004。

如果 VIN 峰值电压为240Vpeak (170Vac)、Vvinac 为0.096V、那么我应该为 kvff 使用0.398?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

嗨、团队:

当使用 AC170~264V、750Vout 进行设计时、根据表1中的注释、kr = 3V/750V = 0.0004。

如果 VIN 峰值电压为240Vpeak (170Vac)、Vvinac 为0.096V、那么我应该为 kvff 使用0.398?

你好小林山,

感谢您关注 UCC28070 PFC 控制器。

由于您的设计专用于仅高压线路输入范围(170~264Vac)、因此我强烈建议您使用 UCC28070A 数据表第35页中修改后的电感器设计流程。 ( https://www.ti.com/lit/gpn/UCC28070A )

尽管 UCC28070和 UCC28070A 几乎相同(低开关频率范围除外)、但最近更新的 UCC28070A 数据表中的所有更新也适用于 UCC28070和 UCC28070-Q1。 (这些数据表和 Excel 计算工具尚未更新。)

您的计算偏离了一个小数点(kr = 3V/750V = 0.004、因此240Vpk 的 Vvinac = 0.96V)、但 您的结论基本正确。

kVFF 应取为0.398。

但是 、我对容差感到关切、因为容差会导致这一结论稍微复杂化。

表1中显示的8个电平的 VINAC 阈值对上升的 RMS 输入电压有效。 随着 RMS 电压的增加、线路峰值电压逐渐超过列出的阈值以改变 kVFF 电平。

为了避免在阈值附近发生"抖动"、RMS 下降电压的阈值是上升阈值的95%。 因此、从2级到1级的 VINAC 阈值是0.95V、而不是1V。 当 kr = 0.004时、170Vrms 的 VINAC 峰值为0.96、略高于但非常接近电平2和电平1之间的下降阈值(0.95V)。

理想情况下、这意味着170Vrms 的 kVFF 应该实际为0.600、因为0.96V 不会超过0.95V 阈值。

我的担心是未指定这些 VINAC 阈值的容差、并且 IC 与 IC 以及批次之间始终存在一些变化。 我认为这些阈值的精度相当严格、但我建议允许5%的裕度、假设最坏情况下 2级和1级之间的下降阈值是0.95V = 0.9025V 的95%。

然后、您可以通过对输入 VINAC 分频器使用 KRI = 3/800 = 0.00375、并仍然对输出 VSENSE 分频器保持 KRO = 0.004、强制170Vrms 的 kVFF 始终为0.398。 这使得设计正确的 Rimo 值更加肯定。

针对 VSENSE 和 VINAC 具有不同的 kr 值的副作用是、电流合成器产生的电流信号下降斜率将关闭约~6%(750/800 = 0.9375)。 这是一个小误差、可以根据经验调整 Rsynth 的计算值以补偿误差。

我建议在指定了最大 THDi 的输入电压下优化 Rsynth;通常这是在230VAC 或200VAC 标称输入电压下。

此致、

Ulrich