工具与软件:

大家好!

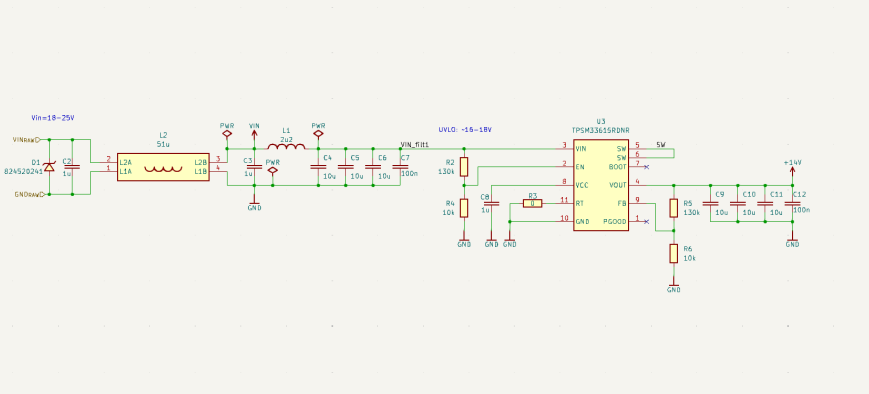

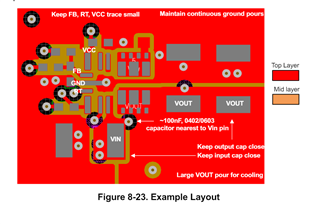

目前、我们使用 TPSM33615RDNR 作为低负载条件下从24V 到14V 的降压转换器。 在我们的标准电路中、RT 引脚上提供了一根跳线、以确保控制器按照建议在2.2 MHz 下运行。

但这会导致大约300mV 的纹波、输入和输出端的频率介于6和10kHz 之间、并且会产生明显的线圈呜呜声。

因此、我们将 RT 引脚连接到 VCC 进行测试、从而解决了该问题。 控制器现在运行在1 MHz 上、最大纹波为30mV。

然而、我们遇到了意外的结果。 当我们允许 RT 悬空时、控制器表现出相同的良好行为。 然而、根据数据表、这不是推荐的做法。

请说明出现这种情况的原因以及行为与数据表不匹配的原因。

我从未在 TI 遇到过类似问题。

此致、

Fabian