工具与软件:

尊敬的 TI 专家:

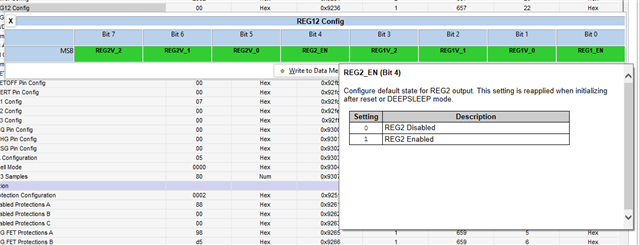

我使用 bq7695202设计了高侧 MOS 驱动解决方案的原理图。 在测试过程中、我发现当 PACK 有一个电压输入(小于 BAT 电压、并且该电压始终存在)时、AFE 的 REG1 LDO 会异常唤醒、但这是 AFE 工作状态的异常唤醒、这会导致功耗约300uA、最终消耗电池电量。

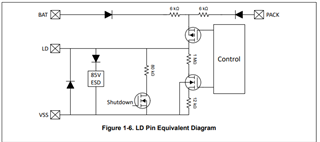

因此、我设想在 LD 引脚上添加一个 PMOS、以控制 LD 引脚输入、防止当 PACK+上存在异常电压时唤醒 AFE 的 REG1 LDO。 软件逻辑是、当我给 BMS 上电以初始化 AFE 时、控制开关会开启 PMOS 并将 LD 引脚打开至 PACK+;当我关闭 AFE 时、控制开关会关闭 PMOS。 这是否会对 DSG 的导通和关断产生影响? 或者您有更好的建议吗? 请告诉我、谢谢。