工具与软件:

各位专家、您好!

LM5146-Q1:并联 MOSFET 时的 FET 损耗计算-电源管理论坛-电源管理- TI E2E 支持论坛

根据上面的讨论、我编写了并联 MOSFET 用例的公式。 为了明确1个 MOSFET 外壳和2个 MOSFET 外壳之间的等式差异、我用红色改变了基准值。

该方程式正确吗? 我对导通、开关、栅极驱动以及体二极管导通有信心、

但是、我对 MOSFET 输出电荷和体二极管反向恢复没有信心。

至于二极管反向恢复、QRR2应随电流变化、如果我在低侧放置2个 MOSFET、它们会分摊电流、因此 QRR2不是恒定的。 我们怎样才能灌输这种影响呢?

至于输出电荷、我不知道该公式是如何推导的。 您能解释一下它的内容吗?

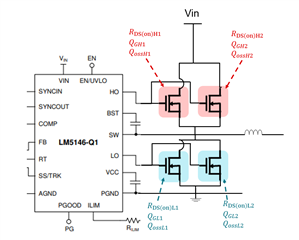

下面是并行配置的图像

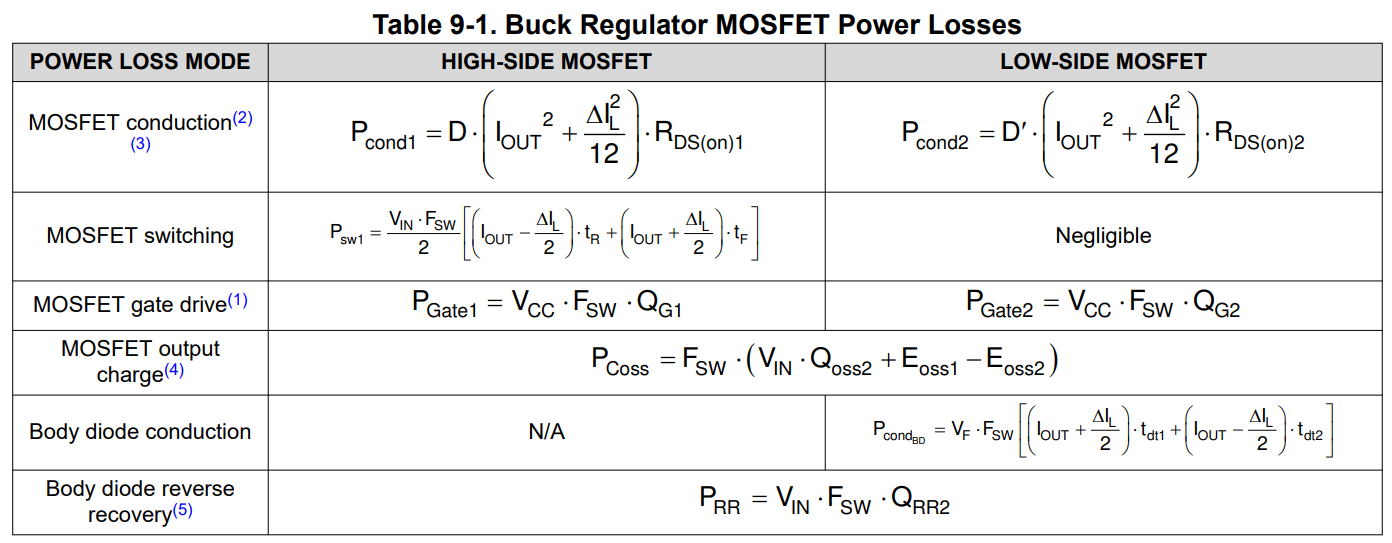

下面是用于非并联配置的公式

谢谢!

Kento