工具与软件:

您好!!

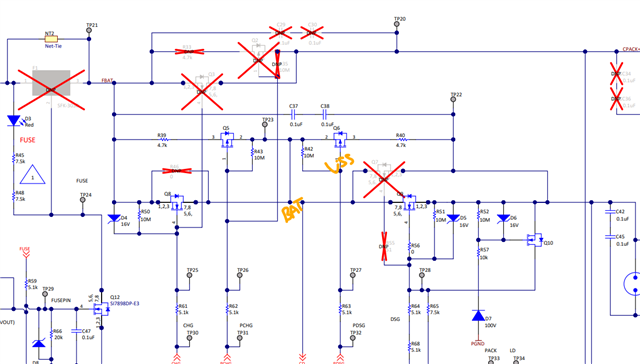

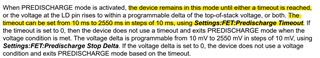

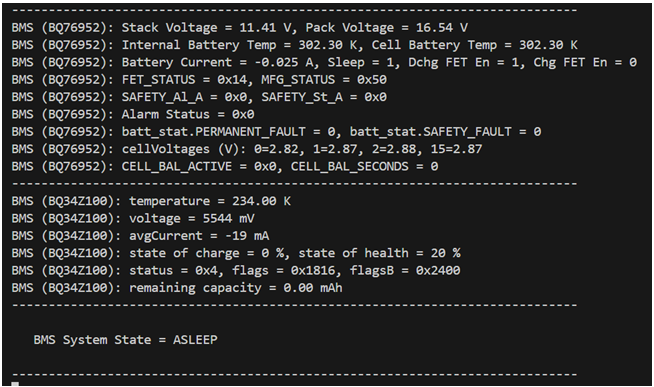

我们在 睡眠模式下的充电器检测存在问题。 当电流足够低(这是 所需的行为)时、我们的 BQ76952器件自动转换到睡眠模式。 当器件转换到 SLEEP 模式时、CHG FET 会自动禁用、这看起来没有问题。 然后、当连接充电器时会有一个明显的 PACK-TOS 增量、但器件未唤醒。 请参阅下面的屏幕截图、其中 电池组电压为11.41V、电池组电压为16.54V、器件保持睡眠状态。 我们将以10mV 为单位向0x9250数据存储器寄存器写入20、这意味着如果 PACK-TOS 增量大于200mV、器件应检测充电器。 但器件没有唤醒。 FET 状态寄存器读数为0x14、0x0057 MFG 状态寄存器读数为0x50。 无有效故障。 通过 PACK-TOS 增量检测到充电器时、是否必须满足其他条件才能唤醒器件?

谢谢!

John