请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:UCC28C43 工具与软件:

这个控制器的最短导通时间是多少?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

高手动、

我已考虑过这项回应、但也许我没有提出正确的问题。 在一个开关周期内、导通 FET 可被打开的最短持续时间是多少? 也就是说、一旦控制器决定开启导通 FET、在控制器决定将其关闭之前、导通 FET 将保持导通的最短时间是多长? 可能该芯片中存在我们尚不了解的内部调节延迟。 我们在这里没有看到零 Atto 秒、即即时关闭。 我们看到我们的工作中出现了最低数量的情况。 请提供建议。

Chrssitopher,

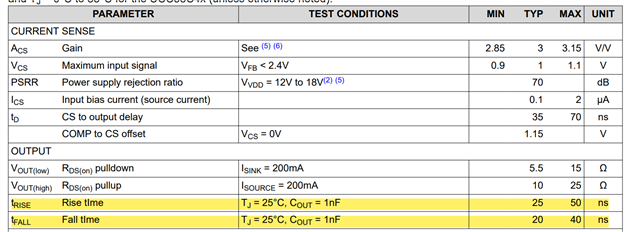

FET 可以打开的最短时间主要取决于命令的控制器占空比(Dmin*fsw )。 然后、您需要考虑栅极驱动器导通和关断 FET 的延迟(请根据 DS 检查以下上升和下降时间)。 您可能还需要考虑从控制器的(OUT-GND)驱动器信号到主 FET 的实际栅极至源极之间的任何延迟(这取决于您的原理图和布局)。 无法提供确切的数字、因为这取决于许多变量。

谢谢你