主题中讨论的其他器件:TPS3436、TPS3436-Q1 、 TPS36

工具与软件:

您好!

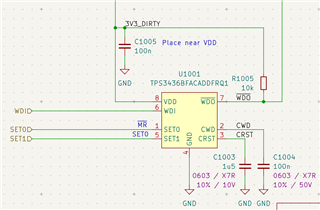

我在使用 TPS35AA17AGADDFR 芯片时遇到问题。 我的 CWD 为100nF、CRST 为1.5uF。 因此、我预计 TWD 为0.495s (TWD=4.95e6 * CWD)、TD 为7.42s (TD = 4.95e6 * CRST)。

这是我的原理图。 我知道它是用于 TPS3436。 我不得不切换以获得可用性。 引脚排列的唯一区别是我将其标记为蓝色的配置引脚。

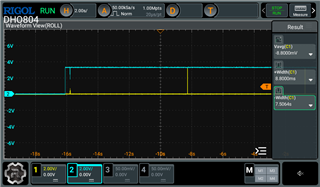

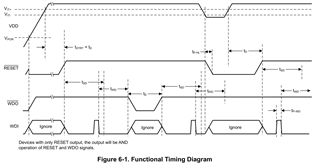

由于 RESET 和 WDO 在此型号中是"与"运算的、因此我希望引脚7在 SSTRT+TD 之前保持低电平。 然后、我希望 TWD 的值较高。 事实并非如此。 当我接通芯片电源时、引脚7保持低电平大约7秒钟。 然后、它仅产生高电平脉冲8ms、并再保持低电平7秒。

为什么复位后 TWD 不保持高电平? 为什么它只在8ms 内保持高电平?

我知道芯片的 TSD 为0、但我仍然希望 TWD 的引脚7在启动后和 TD 之后都为高电平。

我尝试将一个1uF 电容器连接到 CWD、但没有效果。 我还尝试将 SET1拉高(应将 TWD 乘以128)、但也没有效果。

您可以在我的示波器上看到这一点。 Ch1是引脚7、Ch2是 VDD。