工具与软件:

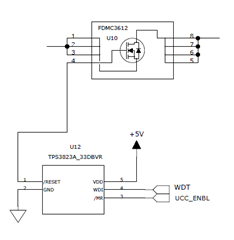

在上面所示的电路中、我尝试在工业应用中使用 TPS3823、以便在/RESET 有效时(即/RESET 变为低电平时)关闭 FET 的栅极。

首先、当 WDI 信号处于高电平或低电平脉冲(我的应用中为1kHz)时、我们将其称为 WDI 信号 CLK。 我的发现是、如果 WDI 保持高电平或低电平、/RESET 输出在标称值上取消置位(高电平)、并大约每1.6秒发出一次短时间的低脉冲。 这似乎是器件的预期运行、但不是我需要的。 当 WDI 未收到 CLK 信号时、我需要/RESET 持续保持低电平。

所需逻辑:

/MR L H H h

WDI X L H CLK

/复位 L L L h

我将尝试修改用于对 WDI 信号去耦的电路(在数据表/3823A 版本中)、但我想我可以使用应用手册或电路建议。

谢谢!