请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS7A49 工具与软件:

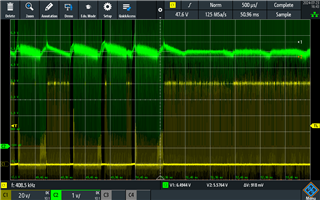

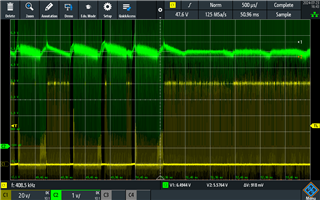

我们将在自举电路中使用该 LDO (15V 至6.5V)为 PSFB ZVT 转换器中的高侧 FET 供电。 在模块切换期间、我们观察到 LDO 间歇性关断。 有关更多详细信息、请参阅随附的原理图和波形。 您能否帮助我们了解发生这种情况的原因以及如何解决这种问题?

CH-1开关节点。

CH-2:引导 LDO 输出。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

我们将在自举电路中使用该 LDO (15V 至6.5V)为 PSFB ZVT 转换器中的高侧 FET 供电。 在模块切换期间、我们观察到 LDO 间歇性关断。 有关更多详细信息、请参阅随附的原理图和波形。 您能否帮助我们了解发生这种情况的原因以及如何解决这种问题?

CH-1开关节点。

CH-2:引导 LDO 输出。

您好!

请检查 LDO 正下方的第一个 PCB 层。 全部是 GND 吗? 或者是否有覆铜连接到 LDO 正下方 FB 引脚周围的另一个信号(例如开关节点)? 如果您可以快照布局、则有助于确认这不是平面层之间的电容耦合。 FB 引脚未被滤波、LDO 中最敏感的节点(不只是这个 LDO、而是任何 LDO)、相邻层上的开关噪声会引起这样的问题。

其他疑难解答建议:

您能否提供 Vin 和 Vout 的差分测量值(相对于浮动 LDO 的 GND)(这样我们就可以看到 Vout 相对于 Vin 的变化情况)?

2.可以尝试降低串联3.3欧姆电阻或者增加并联 Vin 电容(或两者)吗? 我担心 Vin 下降、可能会因触发 Ven 阈值甚至 UVLO 阈值而关闭 LDO。

谢谢!

Stephen