主题中讨论的其他器件: LP87564Q1EVM

工具与软件:

大家好

我们将 LP87564-Q1用于 FPGA 电源、并对 OTP 产品进行原型设计。

PGOOD 寄存器设置为 MASK。

但是、会输出 PGOOD 信号。

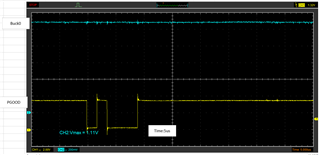

输出波形为10us、比正常的 PGOOD 信号短得多。

我认为这个信号在 IC 的内部栅极电路中是个毛刺脉冲。

请告诉我们您的想法。

提前感谢

浩之

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

大家好

我们将 LP87564-Q1用于 FPGA 电源、并对 OTP 产品进行原型设计。

PGOOD 寄存器设置为 MASK。

但是、会输出 PGOOD 信号。

输出波形为10us、比正常的 PGOOD 信号短得多。

我认为这个信号在 IC 的内部栅极电路中是个毛刺脉冲。

请告诉我们您的想法。

提前感谢

浩之

尊敬的 Fleld:

我已附加两个文件。

" LP8756B2_0x111.txt "是订购 OTP 的说明。

它包含详细器件型号。

"actual register.txt"是从我们正在考虑的电路板的 PMIC 中读取的寄存器文件。

感谢您的合作。

谢谢!

浩之

e2e.ti.com/.../Actual-register.txte2e.ti.com/.../LP8756B2_5F00_0x111.txt

尊敬的裕之:

您能告诉我、您是如何达到这一点的吗? 这是启动、关断、启用器件等吗? 在上述部分/流程中、此过程是否发生一次或每次? 您是否正在更改任何寄存器、如果是、发生在什么时间点以及发生什么情况?

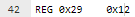

寄存器0x29可能突出显示了一项内容:

这意味着下面的位将是您的电路板的值1、但在该器件的 OTP 中、该位看起来设置为0、因此我在有关上述有关迄今为止所做的进程或尝试的问题上有点困惑。 请在下方注册:

您是否可以重试(通过相应地设置掩码)、但将该位设置为0值并通知我结果? 请告诉我您之前在处理此问题时可能已经测试或更改了哪些内容?

谢谢!

字段中

尊敬的裕之:

这只是在正常运行期间出现的、此时有负载吗?

您是否更改了任何寄存器?如果是、是在什么时候更改?出现了什么?

假设您提供的寄存器转储是在写入寄存器之后(以及如果)、并且存在相应的掩码。 您可以尝试将值0x02写入该寄存器0x29吗?

谢谢!

字段中

大家好、Sarah - San 和 Matt - San、

我希望今天的分析结果可以提供一些线索。

我将产品的 OTP 加载到 LP87564Q1EVM 中、然后 PGOOD 状态被锁存。

PGOOD 似乎始终有效、因为即使在清除它后它也会立即锁存。

EVM 上的负载为零。

我希望您仔细重新检查我之前发送给 Fleld 的 OTO"actual register.txt"。

此致、

浩之

尊敬的 Hiroyuki-san:

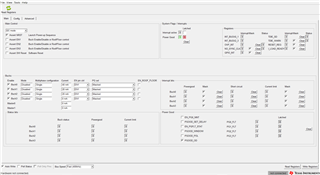

到目前为止、我们做了一项简单的检查、以查看 PG_SEL 屏蔽选项是否适用于 EVM、我们发现当 Buck2 PG2_SEL = 0时、PGOOD 引脚未被 Buck2 PGOOD 故障拉低。 这表明掩码设置正在工作。

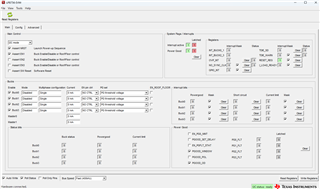

这是我们运行测试之前 GUI 的样子。 我们为所有降压转换器屏蔽了 PGOOD:

我想指出的一点是、只要其中一个降压稳压器报告 PGOOD、顶部的"电源正常"系统标志就会同时显示标志和锁存位的1'b。 这是正常现象、不表示存在 PGOOD 问题。 设置该标志位以指示 PMIC 的输出功率当前处于稳压范围内。 当降压转换器发生问题时、将显示中断位。

即使屏蔽了 PGOOD、您也会在 GUI 顶部看到"Power Good (电源正常)"的1'b。

我仍想尝试并确认、当为 BUCK2屏蔽 PGOOD 时、不应专门指定过压触发 PGOOD 变为低电平、但到目前为止、我们的测试显示、屏蔽位应该会阻止 PGOOD 变为低电平。

此致、

James

尊敬的 Hiroyuki-san:

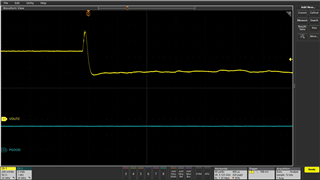

目前正在研究这种范围捕获。

该线程前面提到了寄存器0x29。 您是否已经测试了设置寄存器0x29位5 = 1'b? 这会将 PGOOD 去抖延迟设置为1-11ms、而不是4-8us。

如果您的 PGOOD 因 Buck2上的周期性噪声而被拉至低电平、则较长的去抖时间可能足以忽略噪声尖峰、因此如果您尚未更改该位、请尝试更改该位、并告诉我这是否有任何差异。

如果我可以获得有和没有屏蔽位的 PGOOD 测试的良好图像、我会在后续回复中发布。

此致、

James

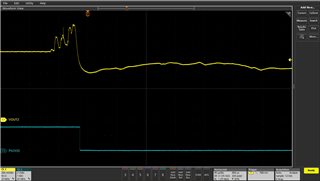

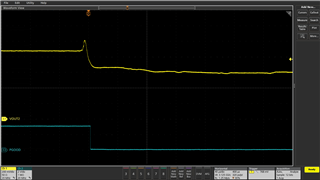

尊敬的 Hiroyuki-san:

这里是我看到的一些 PGOOD 行为示波器捕获。 很难在终端产生与此完全相同的噪声行为、因此我不得不稳定地缩短 FB 路径、以创建不稳定的 Buck2输出。

1) 1)不屏蔽 PGOOD、仅监控 PG 阈值(过压和欠压)

2) 2) PGOOD 未屏蔽、正在监控 PG 阈值和电流限制(过压和欠压)

3) 3)在所有 PG_SEL 寄存器中屏蔽 PGOOD、PG 仍设置为过压和欠压、但预期是 PGOOD 即使在短路事件期间也会保持高电平。

此致、

James

尊敬的 James-San:

感谢您报告验证结果。

我不确定寄存器0x29、所以我再试一次。

哦、测试板的寄存器设置是我之前发送给 Fleld-San 的 OTP 文件吗?

如果测试板上没有负载、通过我们的 OTP 设置、输出电压为850mV、这种现象不太可能出现、那么您能否在500mV 时测试其中一个输出?

然后、将示波器设置为单个触发器、并观察测试板一段时间。

不用急冲测试这些寄存器、您可以在我对寄存器0x29的测试完成后进行测试。

此致、

浩之

尊敬的 Hiroyuki-san:

我上面运行的实验是使用您发送到现场的 OTP 完成的。

[报价 userid="612096" url="~/support/power-management-group/power-management/f/power-management-forum/1383616/lp87564-q1-lp87564-q1-pgood-signal/5348766 #5348766"]如果测试板上没有负载、且我们的 OTP 设置为输出电压为850mV、这种现象不太可能出现、那么您能否在500mV 下测试其中一个 OUTS?我只是想澄清一下、您是指500 mA 应向 Buck2 OUT 施加负载、然后应监控 PGOOD 以查看在 PG_SEL 设置为屏蔽时是否将其拉至低电平?

此致、

James