主题中讨论的其他器件: UCC27511

工具与软件:

您好!

我正在继续主题:UCC21550的半桥电路不能与 Will 配合使用、因为此主题已因无活动超过30天而锁定。

我已将死区时间增加至443ns (R_DT 50K)、但问题仍未解决。

这里还会发生什么情况?

此致、

明亮

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

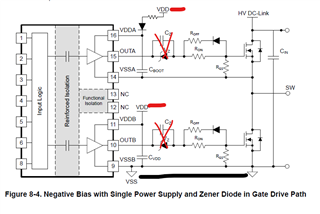

我怀疑 UCC21550数据表第31页中可能提到了这个问题。 我的配置不包括 齐纳二极管具有负 ATE 驱动偏置 . VGS 上有过多的振铃。

第31页

"当非理想 PCB 布局和较长的封装引线(例如、

TO-220和 TO-247型封装)时、电源的栅源驱动电压可能会出现振铃

高 di/dt 和 dv/dt 开关期间关断晶体管。 如果振铃超过阈值电压、则存在风险

意外导通甚至击穿。 在栅极驱动上施加负偏置是一种常用的保持方式

低于阈值时就会出现振铃。 以下是实施负栅极驱动偏置的一些示例"

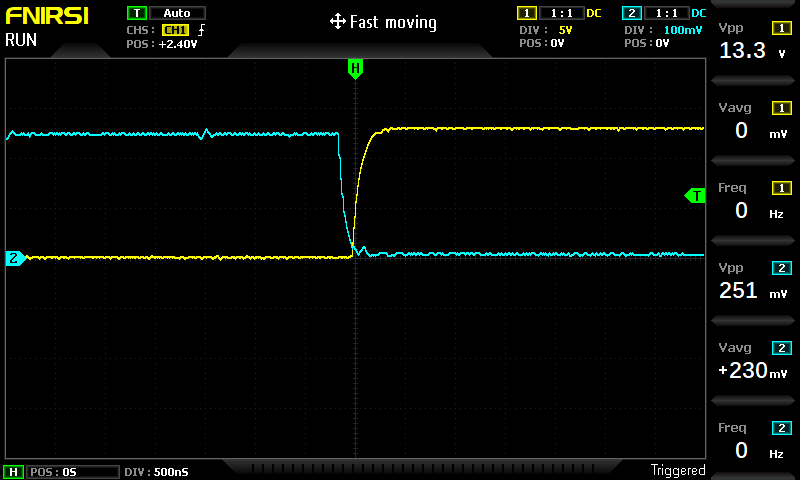

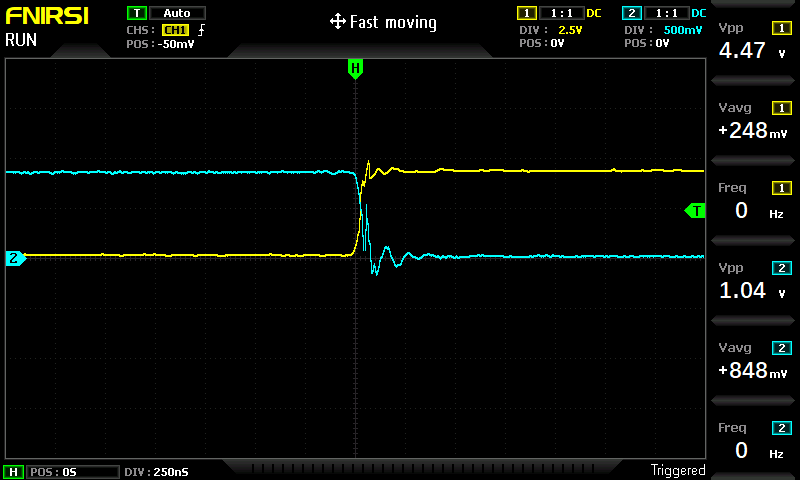

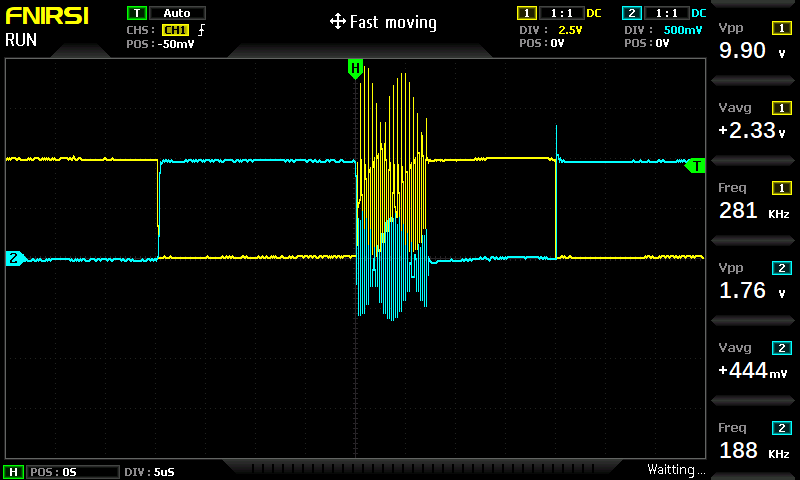

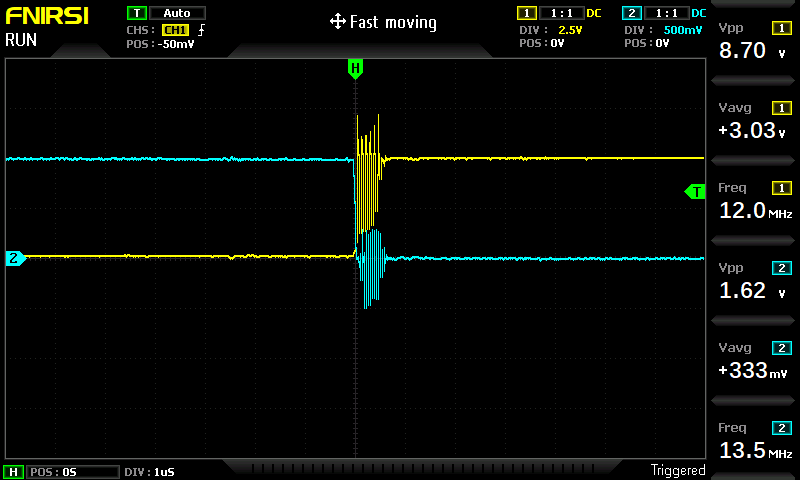

对于低于46V 的直流链路、它开关正常、电流为0.015A、功率耗散为0.4W。 但电路设计和 MOSFET 适用于400V 应用直流链路。 但一旦直流链路增加到 48V 直流、功率耗散就变为20W、并出现温度尖峰、需要立即关闭。 我已经在下拉框链接中附加了测试波形和注释:

Word 文档说明了1-19中的波形图像、以及一个捕获过渡的视频。

此致、

明亮

尊敬的 Bright、

我无法访问下拉框。 您可以在 E2E 上上传并发布图片和文字文档吗?

听起来您有大量的开关节点振铃和米勒尖峰、可导致击穿。 希望您已经获得 VDS 和 Vgs 测量值、以便我们可以确认。 高侧开关闭合时、开关节点电容和 HV 总线电感会导致 VDS 振铃。 通常、我需要在 PCB 上多次重新设定谐振、以便去耦网络可以临界抑制谐振频率。 您在使用什么 FET?

可以通过局部关断缓冲器吸收米勒注入。 我使用正好位于 FET 栅极和源极引脚之间的 UCC27511来缓冲较远的半桥栅极驱动器的低侧。 这样可以更大限度地减小关断电感、并有助于降低 Vgs 上的米勒尖峰。

此外、您可以在开关节点和低侧 FET 之间增加一定距离。 这将增加极少量的电感、有助于吸收低侧的 dvd/dt、从而降低注入的米勒电流。

最后、当开关节点振铃时、HV 总线上的缓冲器将短接至开关节点。 电解电容器可以增加电源轨的电阻和电容、并且体积较大并可以处理热负载、因此可以成为防止开关节点振铃的有效缓冲器。

此致、

Sean

你好、Sean、

负偏置是否需要齐纳二极管? 才能确保将其完全关断?

附加了以下波形:

Word 文档说明了1-19中的波形图像、以及一个捕获过渡的视频。

很好的享受

明亮

e2e.ti.com/.../Waveform-video-capture.MOVe2e.ti.com/.../Waveform-Notes.docx

e2e.ti.com/.../Waveform-video-capture.MOVe2e.ti.com/.../Waveform-Notes.docx

尊敬的 Bright、

齐纳二极管用于钳制电容器 CZ 中充电的电压。 留在 CZ 上的电荷是产生负偏置的偏移电压。

看一下波形、看起来这个噪声由功率级激发。 我们已经看到、一些专为在较低电压下具有极高噪声的高电压应用而设计的 MOSFET。 您是否还有其他任何 MOSFET 可以尝试使用此设置、以查看该设置是否对噪声产生影响?

空载条件下的干净波形以及从44V 到48V 总线电压的突然噪声增加、让我认为这与 MOSFET 有关。

此致、

Hiroki

尊敬的 Hiroki:

感谢您的答复。

在应用中、齐纳二极管和 CZ 的建议值是多少?

此应用适用于直流链路330-390、因此我认为800V MOSFET 应该是可以的。 此外、我需要以5V 增量从小电压测试电路、直到达到直流链路电压。 使用全直流链路电压的第一项测试损坏了电路、因此分级执行时的注意事项。

鉴于应用为330-390V 直流链路、建议使用哪种 MOSFET VDS?

此致、

明亮

尊敬的 Bright、

感谢您的跟进。

1uF 电容器应足以提供~5V 齐纳二极管反向电压。

为 MOSFET 提供较大的裕度非常好、不会出现问题。 我不太熟悉这里使用的 MOSFET、只是想根据过去的经验提供一些输入、介绍高压 MOSFET 在较低电压下的作用。 我最近使用650V Si MOSFET 进行了测试、该测试显示50-300V 的非常高的噪声。

此致、

Hiroki

尊敬的 Bright、

在我的测试中、我能够通过将 MOSFET 交换到不同的 MOSFET (在本例中为 SiC)来完全降低噪声。 大多数噪声被缓解、并且在所有测试的总线电压电平上表现一致

通过其他实验、我发现使用额外的电容器来增加栅源极电容有助于减慢开关速度并降低很多噪声。 MOSFET 栅极上的铁氧体磁珠还有助于防止噪声进入栅极驱动器、如果噪声极高、这可能会导致逻辑干扰。

此致、

Hiroki

尊敬的 Bright、

MOSFET 看起来非常适合您的应用。

1.) 是的、对于栅源电容器而言、这是个不错的值。 ST MOSFET 的输入电容低约336nC、因此该栅源电容器插座有助于在必要时减慢开关速度、以减轻振铃。

2.) 铁氧体磁珠应尽可能靠近栅极放置。 这种铁氧体磁珠不应对开关性能产生任何影响。 阻抗只应在所需噪声频率范围内较高。

以下是一个详细介绍这方面的应用简报: https://www.ti.com/lit/ab/sluaai2/sluaai2.pdf?ts = 1724185330306&ref_url=https%253A%252F%252Fwww.google.com%252F

请参阅 第4页 铁氧体磁珠选择指南。

希望这些解决方案起作用。 请随时提出以下其他问题!

此致、

Hiroki

齐纳二极管有效地降低输出信号。

例如、如果使用18V 电源为栅极驱动器的通道 A 上电、并且使用 Vz = 4.7V 的齐纳二极管、则下拉电压将为-4.7V、上拉电压将在几个周期(CZ 电容器已充电至 Vz)后为13.3V。 必须考虑上拉电压的下移、因为该值在下移后仍应高于 UVLO 阈值。

我相信您的 RC 缓冲器在这里应该够用。 不过、调整 RC 缓冲器值可能值得尝试、从而更大限度地提高效率。

此致、

Hiroki