工具与软件:

您好、请向数据表中添加一些 PG (PGOOD)信息。

当 VIN < UVLO 时、PG 是否会保持高阻态("良好")?

请澄清 PG 启动延迟。 "TPGDLY 28us PG 从高电平到低电平"来自时间戳 VIN 达到 UVLO、"TPGDLY 1ms PG 从低电平到高电平"来自时间戳 VFB 达到"VPGTH VFB 上升(良好)"??

谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好、请向数据表中添加一些 PG (PGOOD)信息。

当 VIN < UVLO 时、PG 是否会保持高阻态("良好")?

请澄清 PG 启动延迟。 "TPGDLY 28us PG 从高电平到低电平"来自时间戳 VIN 达到 UVLO、"TPGDLY 1ms PG 从低电平到高电平"来自时间戳 VFB 达到"VPGTH VFB 上升(良好)"??

谢谢

尊敬的先生:

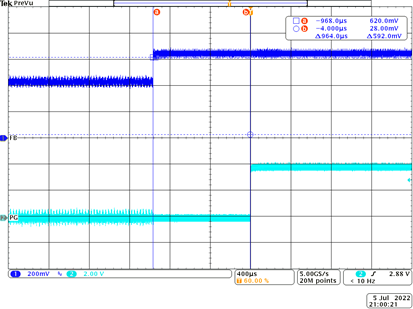

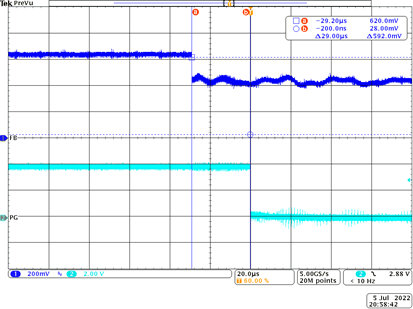

您可以参阅以下波形、更好地了解 PG 延迟时间。

我们将 fb 强制为0.42V 至0.64V 方波。 触发 PG。

您可以从下面的波形中读取到延迟时间约为1ms。 (从低电平到高电平的 PG 延迟)

并将 fb 强制为0.64V 至0.42V 方波。 触发 PG。

您可以从下面的波形看出、延迟时间约为29us。 (从高电平到低电平的 PG 延迟)

现在、如果您再次查看数据表中指定的 PG 延迟时间、我希望它可以帮助您更好地了解它。

谢谢!

BRS

卢西亚