Other Parts Discussed in Thread: BQ2970

工具与软件:

您好!

我们担心使用双 BQ2970进行双重保护时最终可能处于额外泄漏的状态。 会尝试解释推理,以得到你的想法这。

BQ2970数据表的第8.4.4章说明了以下内容:

"在放电过流状态下、V–和 VSS 引脚由恒定电流阱 I_V–S 连接 当发生这种情况并且连接了负载时、V–引脚处于 BAT 电势。 如果负载断开、则 V–引脚进入 VSS (BAT/2)电势。

V–和 BAT 之间的电阻 R_V–D 在放电过流检测状态下未连接。"

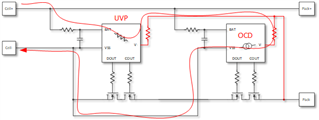

一些 PCM 通过直接复制安全 IC 和串联的放电/充电 FET 来实现双保护(针对单路故障处理)。 然后、两个 IC 的 V-引脚连接到同一个 PACK-节点(通过其自己的2.2k)。 如果 IC 检测到过放电、该 IC 的 V-引脚将通过内部 R_V–D 拉至 BAT 电位

请参阅下面的原理图。

问题:

1) 1)当一个 IC 进入过放电状态时、是否存在以下风险:该 IC 的 V-引脚拉至 BAT 会在检测到过放电之前将另一个 IC 的 V-引脚拉至高电平、从而触发另一个 IC 的放电过流状态?

2) 2)如果一个 IC 进入过放电状态、而另一个 IC 进入放电过流状态、则电流路径 IC1 BAT > IC1 V-> IC2 V-> IC2 VSS 是否存在泄漏的风险(如原理图中的红色箭头所示)?

3)还是不会发生这种情况(IC1过放电拉取 IC2 V-生成错误的 IC2放电过流状态和泄漏路径)? 例如、由于 R_V-D ~300k Ω、因此 V-节点将为 BAT - 1V、并且已经是1/300k = 3.3uA、这小于 I_V-S 灌电流的最小电流、如果从一开始就发生这种情况、会导致 IC2保留放电过流状态?

4)在文本"V–引脚进入 VSS (BAT/2)电位。" 假设这些电位以 PACK-为基准、您可以详细说明 VSS = BAT/2的产生方式吗? 这是否指何时恢复到正常状态(考虑到 BAT/2 < BAT - 1V、从而释放放电过流状态)?

5) 5)如果在一个时间段内发生多种情况(例如放电过流和过度放电)、那么最先发生的情况胜出、然后 IC 保持该状态、直到由于所述状态的释放条件而被释放? 或者是否有任何其他优先级激励?