工具与软件:

嗨、团队:

当 VCC = 0V 时、GDA 和 GDB 是否下拉至 GND?

如果我拉高 GDA 和 GDB、它们是否不会变为高电平?

此致、

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Hirotsugu-san、

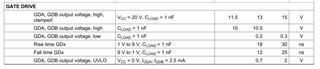

当 VCC = 0时、在 UCC28070的每个栅极驱动电路中都有一个小型自偏置的 P 沟道或 PNP 晶体管、在 GDX 上形成弱下拉。 该器件能够消耗低电平电流(~μ A 2.5mA)、从而在交流线路上发生通过 MOSFET Crss 耦合的低电平瞬态干扰时使主 MOSFET 保持关断状态。

这些下拉电阻不能传导高电流、可能会被高电流上拉电阻和低阻抗电压源过载。

当施加 VCC >~2V 时、这些引脚会内部禁用。

此致、

Ulrich

Hi Hirotsugu-san、

我现在更好地理解您原来的问题。

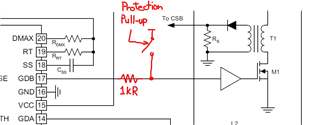

特殊保护电路的强上拉可能会在 VCC = 0V 时出现 UCC28070栅极驱动弱下拉、但在0V < VCC < 8.8V 时上拉必须非常强

UCC28070栅极驱动器未被额定直接驱动 MOSFET、预计栅极驱动 IC 或缓冲器电路将被用于将 GDX 输出连接至 PFC MOSFET。 然而、GDX 输出实际上是实际的栅极驱动器、根据不同的 IC 进行调整、并在 VCC >~2V 时具有显著的下拉强度。 目前还不清楚在什么 VCC 电压下、下拉强度变得很重要;可能在1V < VCC <3V 之间。

确切值不重要、可能会因 IC 和 IC 而异。 重要的是、当 UCC28070上的 VCC 大于0V 时、即使小于8.8V、也可能要求特殊保护电路出于某种原因而采取行动。 在这种情况下、直接保护上拉电阻将面临来自 UCC28070驱动器输出的相当低阻抗的下拉电阻。

为了避免这种情况、我建议在每个 GDX 上串联一个1KR 电阻、以便保护上拉电路只能驱动1KR 负载(大约)。

由于输入引脚电容(例如、通常为5pF)、1KR 串联电阻器不会为发送到栅极驱动器 IC 的正常 PWM 信号产生显著的延时时间。 1KR 将限制电流、从而不会损坏 UCC28070。

较低的串联电阻值将进一步降低 PWM 时间延迟、但会允许更高的下拉驱动器电流。 在某个较低的电阻下、栅极驱动损坏的风险变得很大。 您的客户可以在最小化 PWM 延迟时间和最小化保护电路拉动强度之间进行权衡。

此致、

Ulrich