主题中讨论的其他器件:MSP430F5529、 TPS92633-Q1

工具与软件:

您好!

我们可以连接吗 2个 IC、每个 IC 6个 PWM 引脚 并行连接到 MSP430F5529的单个 GPIO 引脚?

它是否会按预期工作?

此致、

德州仪器(TI

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

您好!

我们可以连接吗 2个 IC、每个 IC 6个 PWM 引脚 并行连接到 MSP430F5529的单个 GPIO 引脚?

它是否会按预期工作?

此致、

德州仪器(TI

尊敬的 Tex:

是的、您可以并联多个 PWM 引脚、通过单个 GPIO 引脚控制调光。

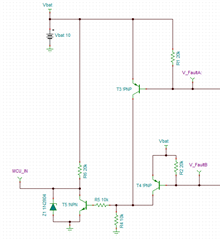

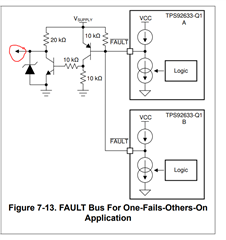

我记得在您之前的查询中、您想在"连带失效、其他开启"故障总线配置中连接这2个 IC。 如果是、请注意 TPS92633-Q1数据表的图7-13中存在误差。 为了将器件配置为连带失效模式、您需要在每个 FAULT 引脚上连接一个单独的 PNP 晶体管和上拉电阻器、如下面的原理图所示。

我已经附上了完整的 TINA-TI 仿真文件供您参考。

e2e.ti.com/.../One_2D00_Fail_2D00_Others_2D00_On.TSC

祝您继续进行设计。

此致、

Zach

尊敬的 Zach:

很抱歉响应延迟、

请澄清与故障 PIN 相关的一些问题

原理图是图7-13、实际正确。

那么、我可以按原样实施该电路吗?

1.您能解释一下图7-13中提到的电路是如何工作的吗?

2.在图7-13中,他们用2个 IC 到单电路,我可以用4个 IC 到单电路吗?

3.为什么 MCU 连接在您之前的电路中?

4.那么、根据您之前的电路、这个引脚也将被连接至 MCU 作为输入?

5. 该电路是否能在没有控制器的情况下工作?

6.您能否说明一下这些组件的器件型号和电阻器容差、如果您有任何使用 TPS92633-Q1实现此电路的设计/原理图文件、请分享。

此致、

德州仪器(TI

尊敬的 Tex:

1.您能解释一下图7-13中提到的电路是如何工作的吗?

FAULT 引脚连接到内部3mA 下拉灌电流。 ~期间、Δ V 3mA 被拉过 PNP 的基极、从而导通晶体管并将 集电极拉至高电平。 当 PNP 的集电极为高电平时、NPN 晶体管也会导通并切换 MCU 输入端的电压、以指示发生了故障。 PNP 上的0.7V 发射极至基极压降使共享故障总线保持高电平、从而在一个器件发生故障时使其他器件保持开启状态。 这是一个连带失效其他导通应用。

2.在图7-13中,他们用2个 IC 到单电路,我可以用4个 IC 到单电路吗?

可以、使用4个具有共享故障总线的 IC。

3.为什么 MCU 连接在您之前的电路中?

发生故障时回读。

4.那么、根据您之前的电路、这个引脚也将被连接至 MCU 作为输入?

如果您希望使用 MCU 在发生故障时进行回读、此引脚将连接到 MCU 输入。 这是典型的应用。

5. 该电路是否没有控制器?

对于连带失效和其他导通功能、MCU 用于监测是否发生故障。

6.您能否说明一下这些组件的器件型号和电阻器容差、如果您有任何使用 TPS92633-Q1实现此电路的设计/原理图文件、请分享。

选择最大 VCE 电压大于电池电压的晶体管。 1%电阻。

这是我更新后的 TINA-TI 仿真文件。

e2e.ti.com/.../One_2D00_Fail_2D00_Others_2D00_On_5F00_3mA。TSC

此致、

Zach

尊敬的 Tex:

1.为什么 在故障情况下使用电流发生器?

电流发生器用于模拟 TPS92633-Q1 FAULT 引脚的3mA 内部下拉。 这是一个比我之前的开漏配置更精确的模型。 请注意、图7-13显示了连接到 FAULT 逻辑的内部灌电流。

2.为什么两个 IC 的电压都降低,而故障仅在1 IC 中?

在 PNP 上的0.7V 发射极至基极压降会降低电压。 这种压降发生在两个故障引脚上、因为它们直接连接在一起。 即使压降很小、故障总线仍保持逻辑高电平、从而使另一个器件保持有效状态(一个器件失效其他器件导通)。

这是一种简单而巧妙的解决方案、依赖于内部电流阱以及 PNP 是电流控制器件这一事实。

我希望这对您有所帮助。

此致、

Zach