主题中讨论的其他器件:、 CSD19535KTT、CSD19532Q5B

工具与软件:

您好!

我的客户请求 TI 对 TPS23523设计进行审核。

请查看以下内容:

e2e.ti.com/.../TPS23523_5F00_review_5F00_241108.pdf

问题1。 请检查该客户的电路是否有问题。

问题2: TPS23523EVM-863用户指南列出了电流限制设置为12.5A。 根据 EVM 的电路设计、ICL1 = VSNS、CL1/RSNS = 40mV/2m Ω= 20A。 请告诉我们如何计算12.5A。

问题3。 EVM 的 SNS 引脚通过100 Ω 连接到 VEE。 请告诉我们为什么需要此连接。

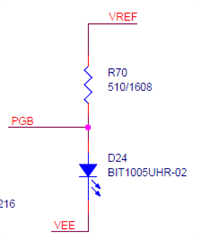

问题4。 您能否告知下面的 PGB 引脚连接电路是否正常?

问题5. 根据100W 负载、是否可以将连接到栅极的 FET (CSD19535KTT)更改为连接到 GATE2的 FET (CSD19532Q5B)? 对于这一点、除了 FET 的功率和电流之外、是否还有其他需要考虑的因素?

提前感谢。

JH