工具与软件:

测试条件:812VDC、 满载43A @输出电压23.5V

以下是不同负载和不同延迟下的图像。 我将使用不同的延迟和不同的匀场值进行测试。

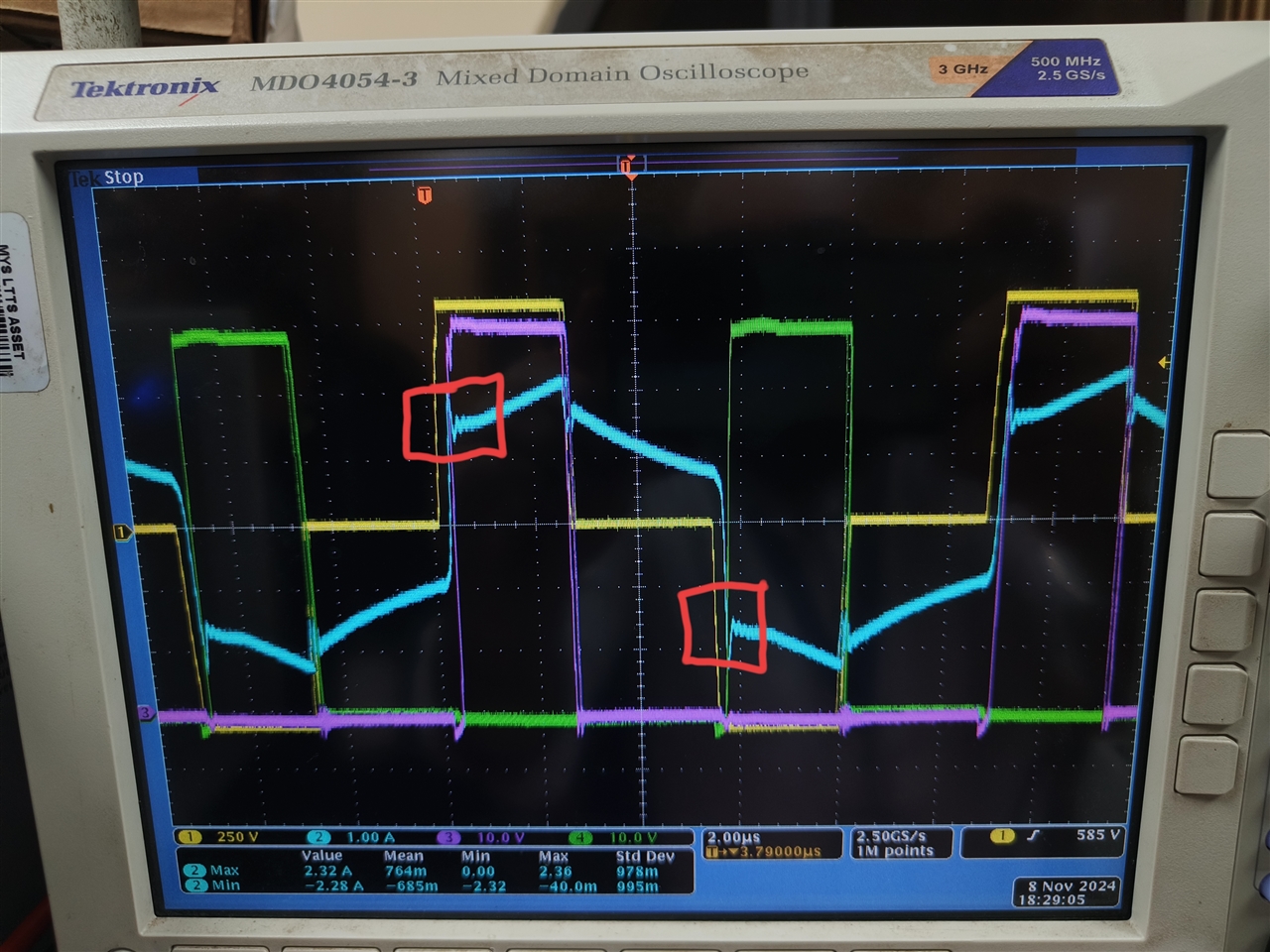

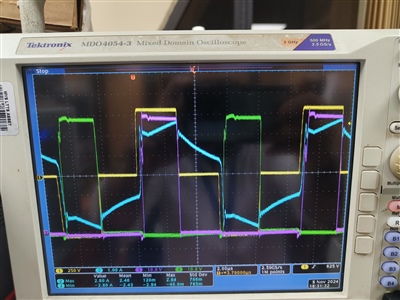

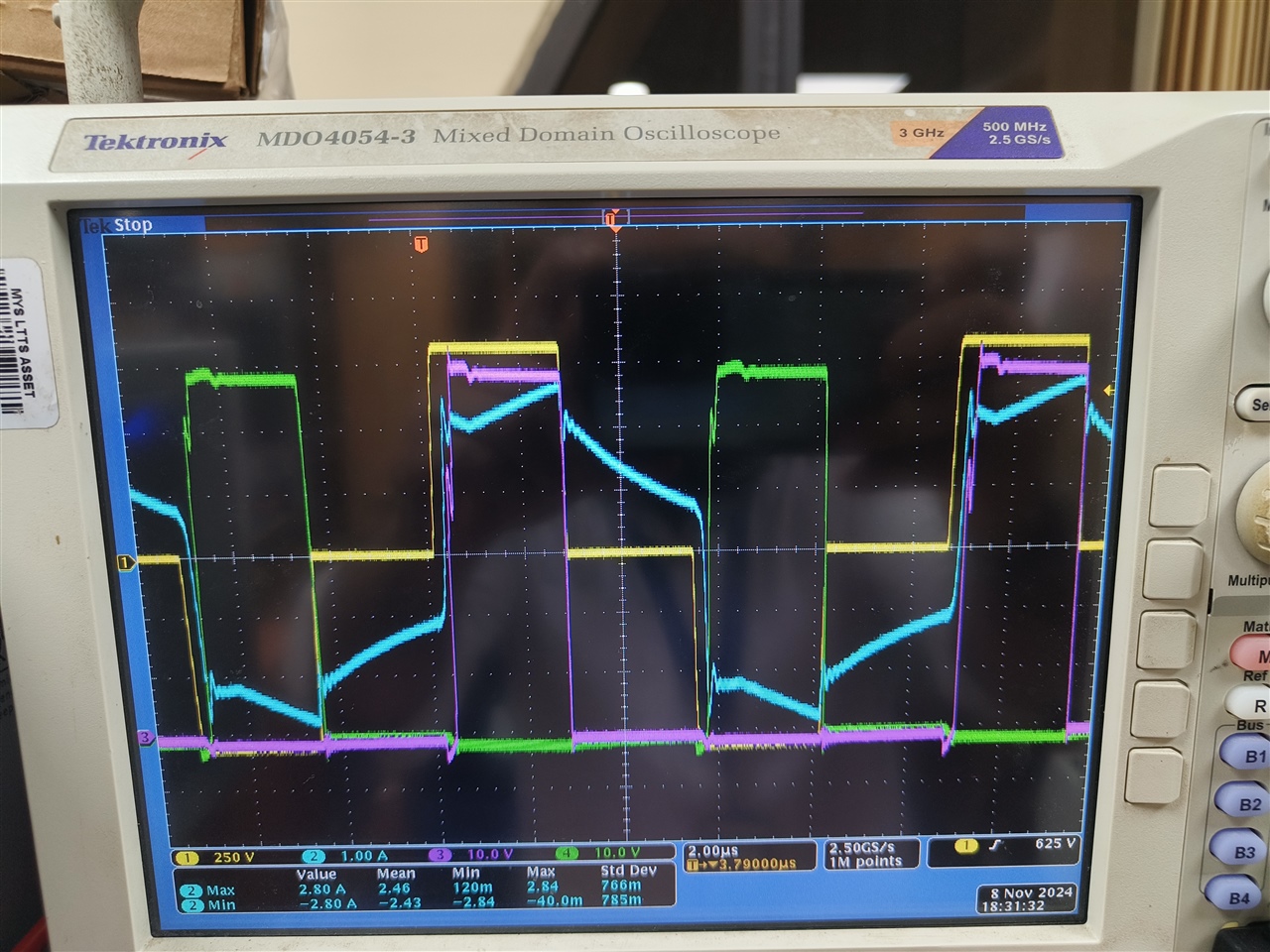

黄色:变压器初级电压

蓝色:变压器初级电流

紫色、绿色:同步 FET 漏极源极

1.输入电压: 812 VDC, DELAB : 8.2K , DELCD: 8.2K , DELEF : 8.2K

负载:25.8A、Llkg +垫片:22.6uH + 20uH

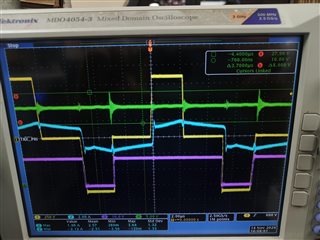

2. VIN:812 VDC, DELAB :8.2K , DELCD:8.2K , DELEF:8.2K

负载:25.8A、Llkg +垫片:22.6uH + 30uH

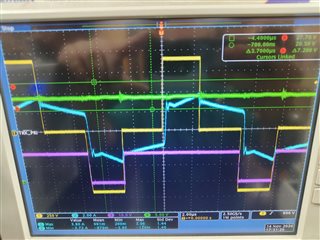

3. VIN : 812 VDC, DELAB : 8.2K , DELCD: 8.2K , DELEF : 8.2K

负载:33A、Llkg +垫片:22.6uH + 30uH

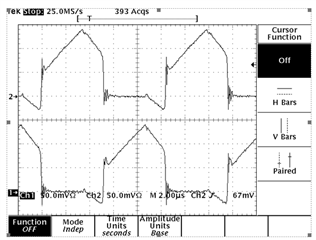

我想了解平坦的区域在电流和为什么下降在该区域通过增加电流. 为使设计更好而正在发生的情况以及可以采取的其他措施。 ?