工具与软件:

Dears、

在客户的前一版本中、FPGA 内核由 LDO 供电。 为了降低功耗、客户现在希望使用 DCDC:TLV62568作为电源。

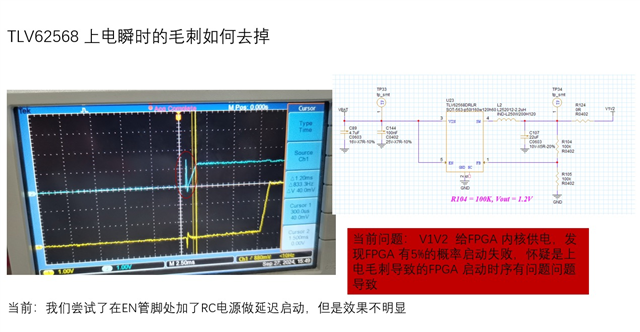

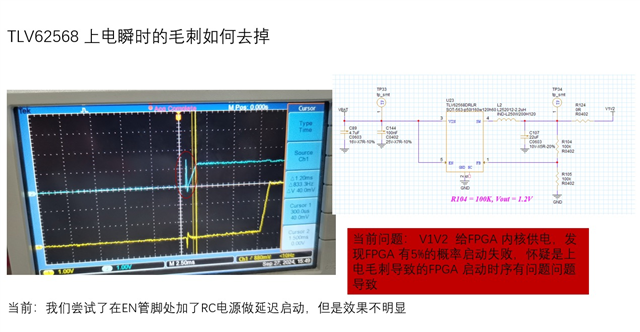

当前问题:使用 V1V1为 FPGA 供电、发现 FPGA 有5%的可能性无法启动。 怀疑 FPGA 启动时序是由上电干扰引起的。 请帮助分析原因。

此外、客户目前尝试在 EN 引脚上添加 RC 电源来延迟启动、但效果不明显。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

Dears、

在客户的前一版本中、FPGA 内核由 LDO 供电。 为了降低功耗、客户现在希望使用 DCDC:TLV62568作为电源。

当前问题:使用 V1V1为 FPGA 供电、发现 FPGA 有5%的可能性无法启动。 怀疑 FPGA 启动时序是由上电干扰引起的。 请帮助分析原因。

此外、客户目前尝试在 EN 引脚上添加 RC 电源来延迟启动、但效果不明显。

您好、Josef

蓝色的是1.2V 输出电压(3.3V 具有慢启动)、两个电压输入都直接连接到外部电源(通过 PMOS 反向连接电路、MOS 的 D 连接到电源、S 连接作为电源输出)。 我强烈怀疑直流/直流输入电容器充电刚刚达到 CE 使能阈值、这会触发直流/直流转换器进入工作状态、然后直流/直流转换器出于某种原因再次进入关断状态?

(我已在原稿英文图片中描述了所有中文内容)

此致、

Arabella

还有几个问题

1. tlv62568的 FB 引脚输入电流是多少? 知道了该值、客户可以更准确地计算反馈电阻并估算输出电压。

2. tlv61070的 FB 引脚的输入电流是多少? tlv61070的 FB 引脚的输入电流大于盛邦威6603的输入电流。 在某些情况下、相互更换时必须修改分压电阻。

3.客户最初计划使用 tlv62568为 FPGA 内核供电,但有5%的可能性 FPGA 无法启动。 目前只能切换回 LDO 电源解决方案。 如果您有好主意、请提供您的建议。

非常感谢

还有几个问题

1. tlv62568的 FB 引脚输入电流是多少? 知道了该值、客户可以更准确地计算反馈电阻并估算输出电压。

2. tlv61070的 FB 引脚的输入电流是多少? tlv61070的 FB 引脚的输入电流大于盛邦威6603的输入电流。 在某些情况下、相互更换时必须修改分压电阻。

3.客户最初计划使用 tlv62568为 FPGA 内核供电,但有5%的可能性 FPGA 无法启动。 目前只能切换回 LDO 电源解决方案。 如果您有好主意、请提供您的建议。