工具与软件:

你好。

为使 UCC28064A 在连续单相模式下运行、将 PHB 输入连接至 VREF 以禁用 B 相运行。 此外、线圈断开连接、ZCDB 信号不会产生任何东西。 虽然它是在单模式下运行、但我有两个问题。

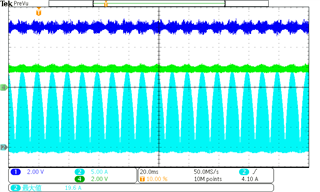

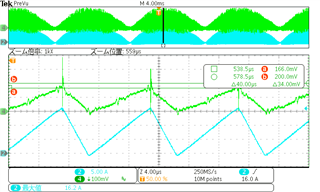

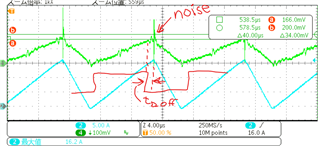

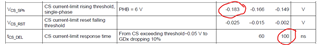

首先是 CS 引脚输入端的峰值电流限制阈值未从双模(0.2V)更改为单模(0.166V)。 我知道启动时阈值为0.2V、并且在 Vinac 的14线路半个周期后、阈值变为0.166V。

在电流电路板上、电流检测电阻为12mΩ、峰值电流计算为16.6A (启动时)/13.8A (稳态)、但当我在实际器件上操作电路板时、在启动和稳态下的峰值电流均为16.6A。 是否有办法解决此问题?

其次、我想知道如何确定单一模式下的最佳 Rtset。

谢谢。