请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:UCC21225A 工具与软件:

大家好、团队成员:

在过流情况下、负电压尖峰将超过-2V 绝对最大值、并在20ns 内达到-6V、这是否允许? 如果没有、允许的最大值是多少? 提前感谢。

BRS、

Francis

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

大家好、团队成员:

在过流情况下、负电压尖峰将超过-2V 绝对最大值、并在20ns 内达到-6V、这是否允许? 如果没有、允许的最大值是多少? 提前感谢。

BRS、

Francis

尊敬的 Francis:

2V 额定值是为了防止内部 ESD 二极管因吸收过多功率而受损。

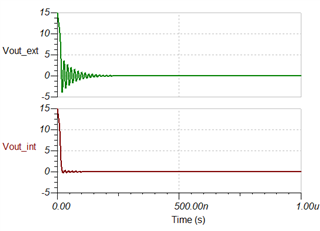

输出键合线和输出负载电容形成了寄生 LC 结构。 由于这种 LC 谐振结构、输出级的上升时间和下降时间非常短、可能会在电容器负载上产生过冲和下冲。 虽然这会 在 Vout_ext 上产生短暂的瞬态、但内部电压 Vout_int 通过一个闭合的 FET 很好地钳位到 VDD 或 VSS、而内部晶体管上的电压(我下面原理图中的 T1和 T2)实际上要低得多。

我已在输出引脚上测量到高达-10V 的负瞬态、而不会损坏栅极驱动器。 如下所示、外部电压下冲随着串联电阻的增加而降低。 此瞬态不应超过驱动型 FET 栅极的 Vgs 额定值仍然很重要。

此致、

Sean