请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:UCC21750 工具与软件:

您好!

我在使用 SIC 器件 PN:C3M0040120K ( 2个并联)的2L 三相逆变器(25kVA)中使用 UCC21750 +UCC15241时遇到了问题。

有关 该项目的一些重要信息:

- 输出功率= 25kVA。

- 输出电感= 196uH。

- 输出电压= 220-240V (相位到中性点)。

- 开关频率:45kHZ。

- 直流总线电压= 830V。

- VDD COM = 15V。

- VEE COM =-4V。

- 电源管理类产品(VCC)-GND = 5V。

关于该问题:

当转换器在标称负载或超过80%的情况下运行时、有时会触发 RDY (UVLO)信号、但电源电压电平似乎没有问题。

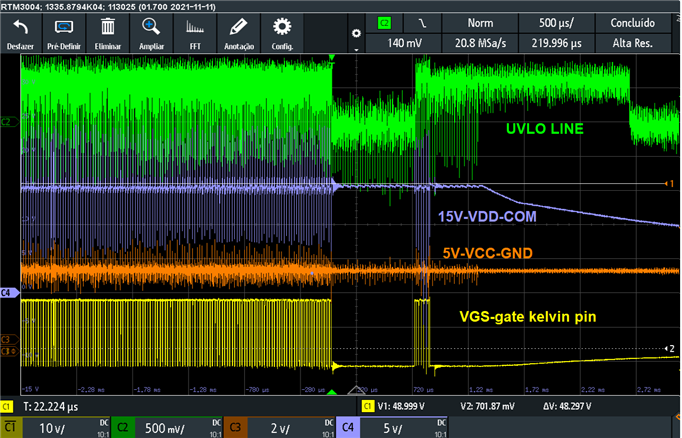

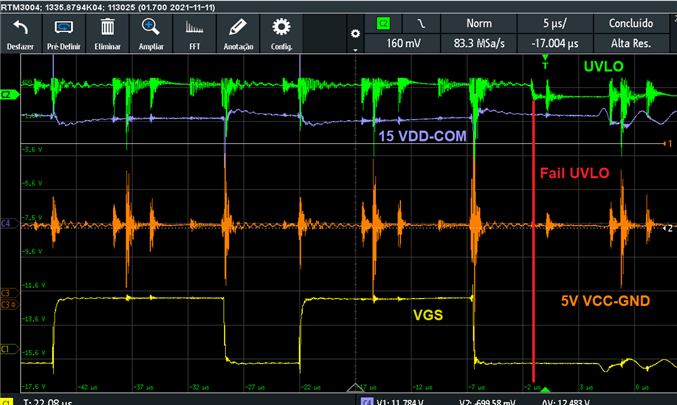

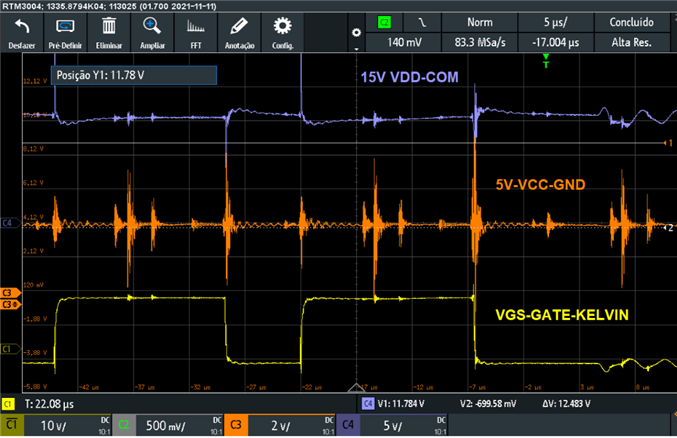

在下面的波形中、可以观察到 UVLO 线被拉低(绿色)、开关命令停止同时工作(黄色)。

用蓝色和红色显示的内容可以观察到 VDD (15V)和 VCC (5V)电压、看起来没有问题。

该问题仅在死区时间小于400ns 时发生。 死区时间为400ns 时、不会观察到该问题。

这似乎是一个噪音问题,但我想知道,是否有人已经面临一些类似的问题。

谢谢!