工具与软件:

大家好、

我将 UCC21330B-Q1用作电机控制器单元逆变器中的栅极驱动器。 虽然栅极脉冲在正常运行期间正常工作、但我在启动期间遇到了一个问题。 在微控制器开始运行并发送 PWM 输入(栅极驱动器无输入)之前、高侧输出(OUTA)保持在恒定的9V、低侧输出(OUTB)保持低电平。

为了进行调试、我已将 DISABLE 引脚和 DT 引脚连接至低电平。 不过、这种默认行为会出现问题、因为除非输入端接收到脉冲、否则高侧和低侧输出都应默认保持低电平。

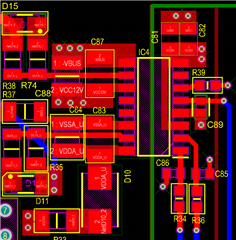

如何解决此问题? 我已附上下面的原理图: