工具与软件:

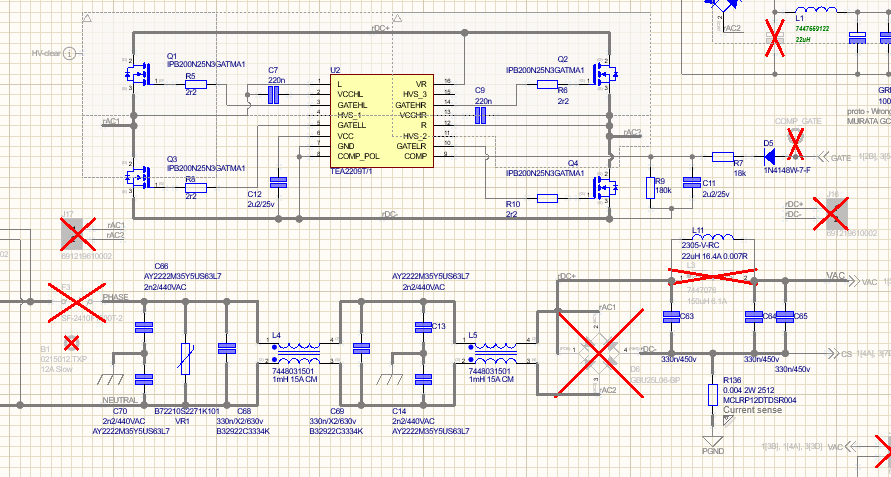

大家好、我的 PFC 电路运行电压为115V 交流电压、可产生400V 直流 电压。目标输出功率约为700W、一旦一切正常运行、我会将电路加倍、以获得1.2kW+

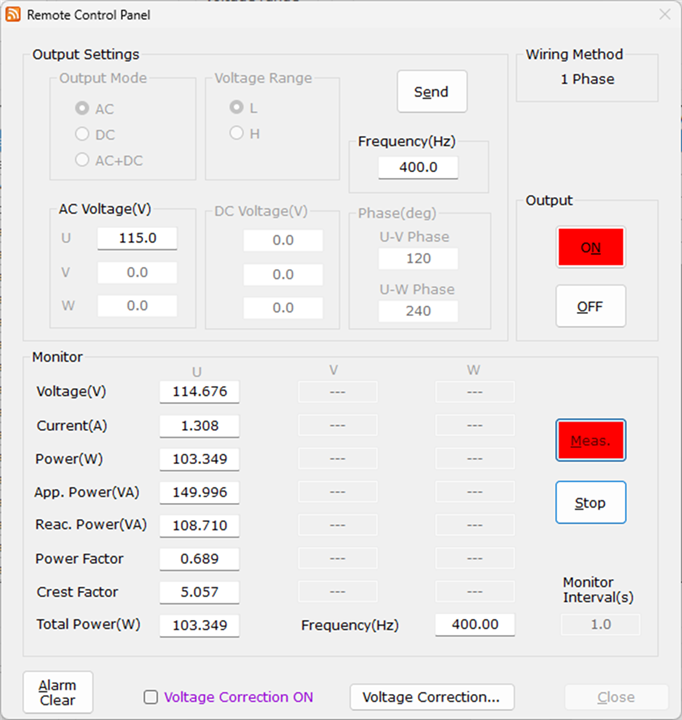

目前、我的 PF 数字太糟糕了(空载时约为0.3、在200W 左右时峰值为0.7、在500W 以上时回落至约0.5)

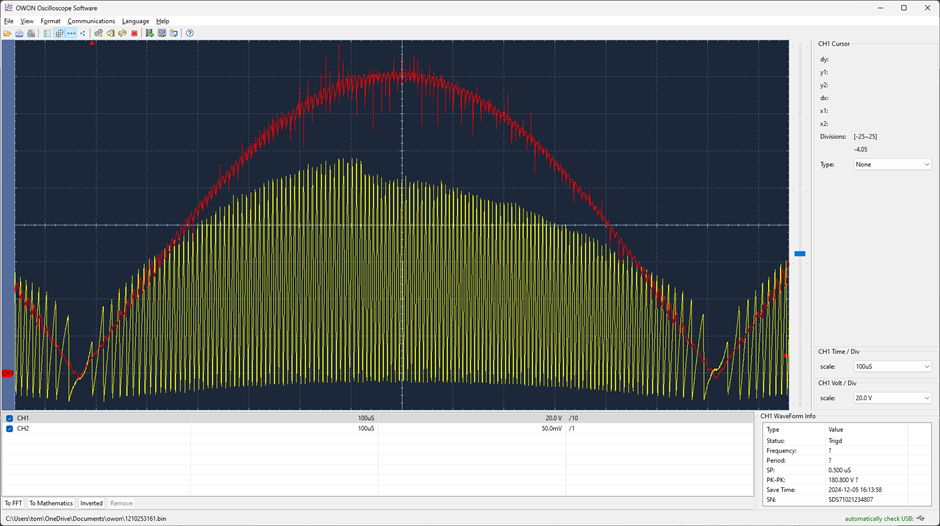

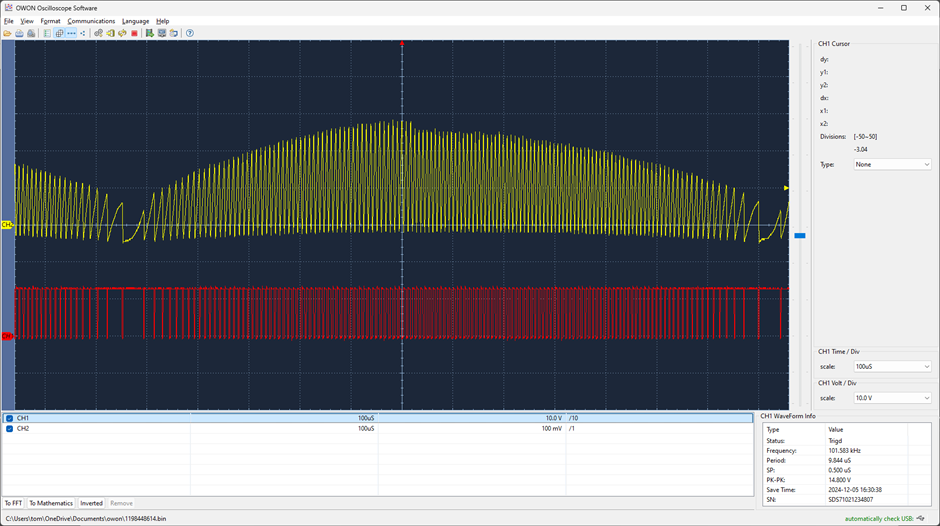

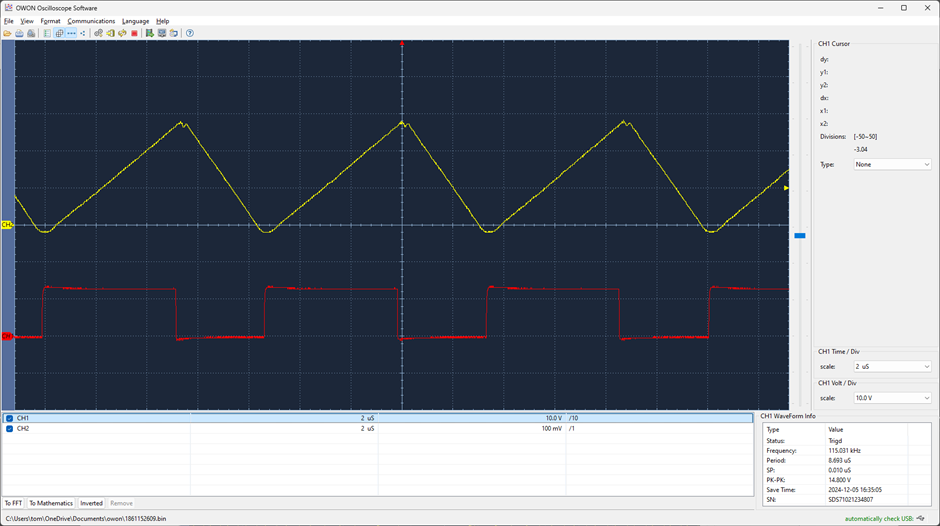

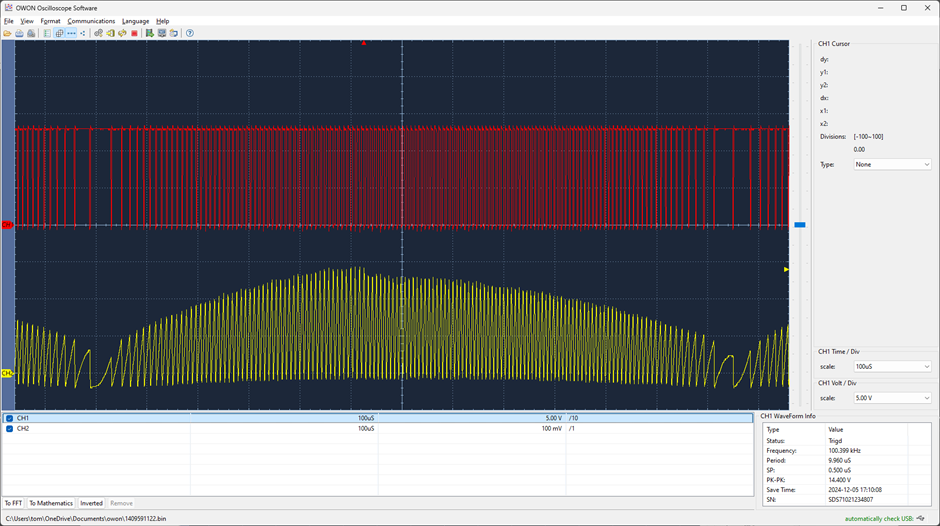

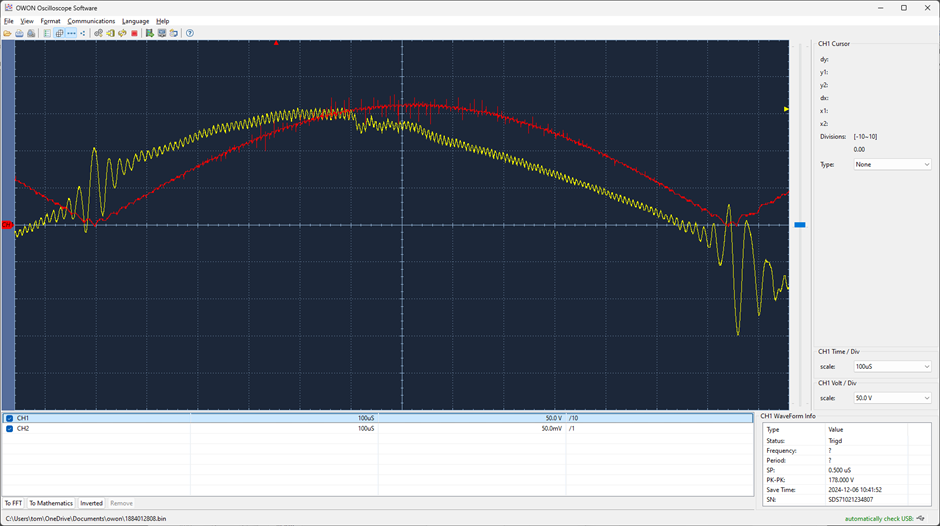

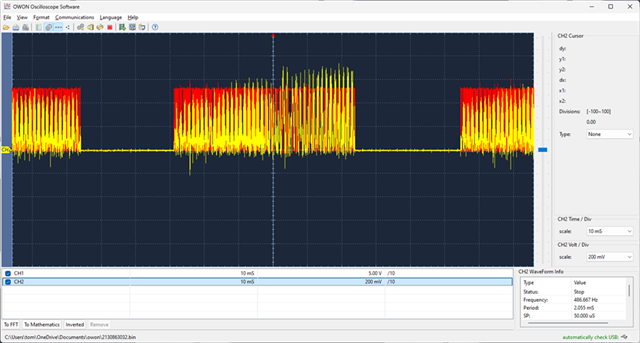

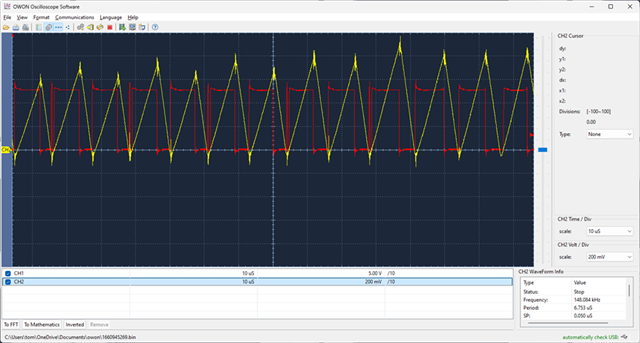

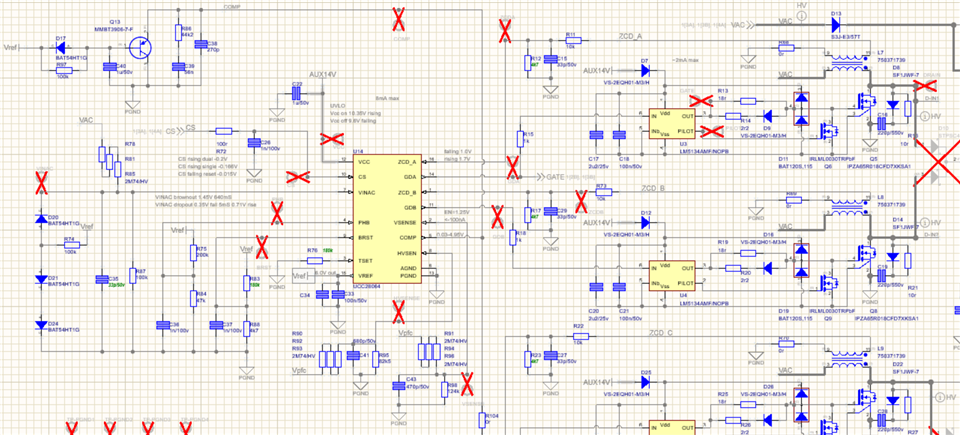

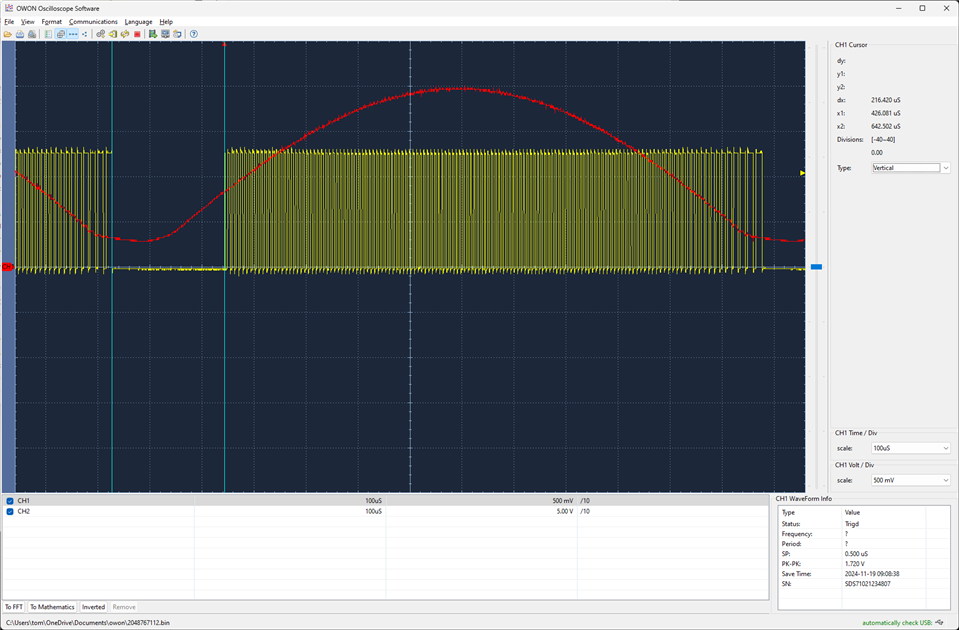

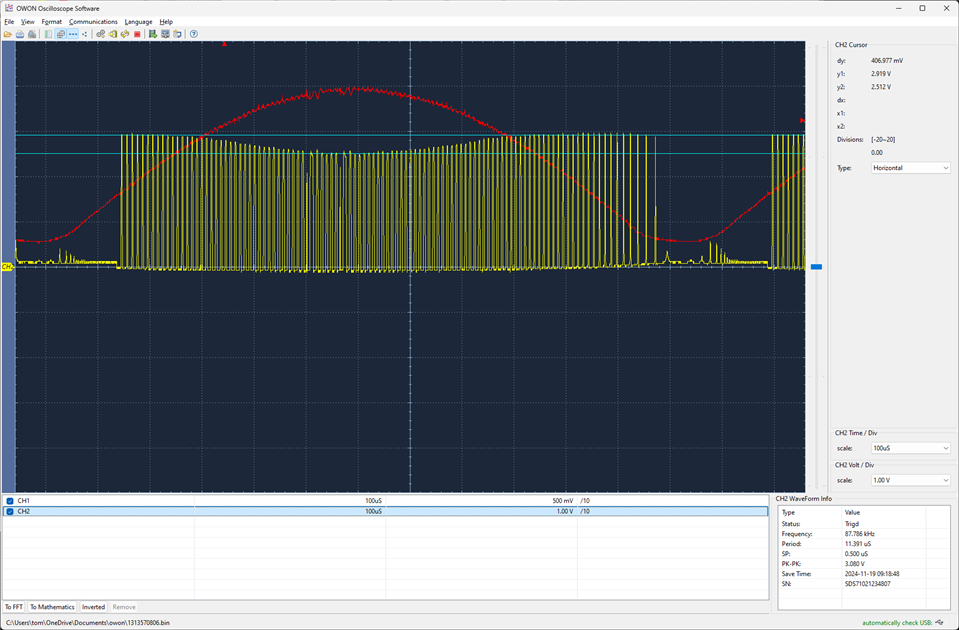

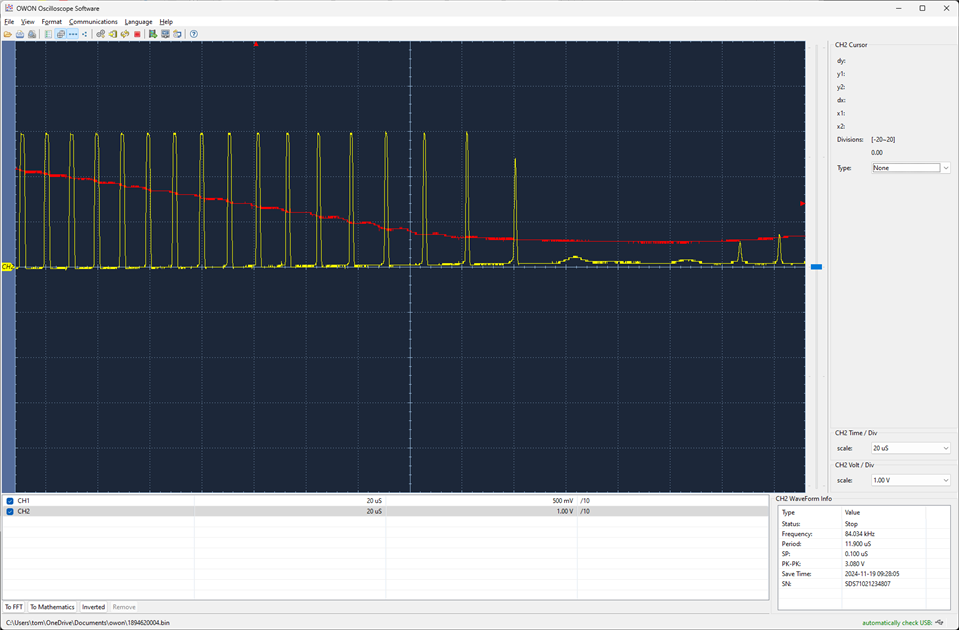

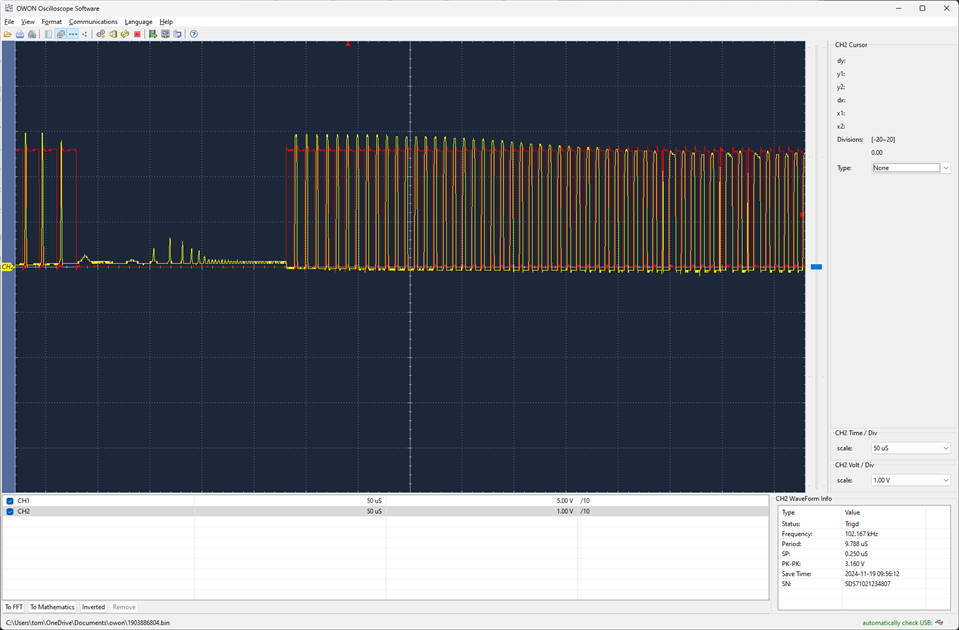

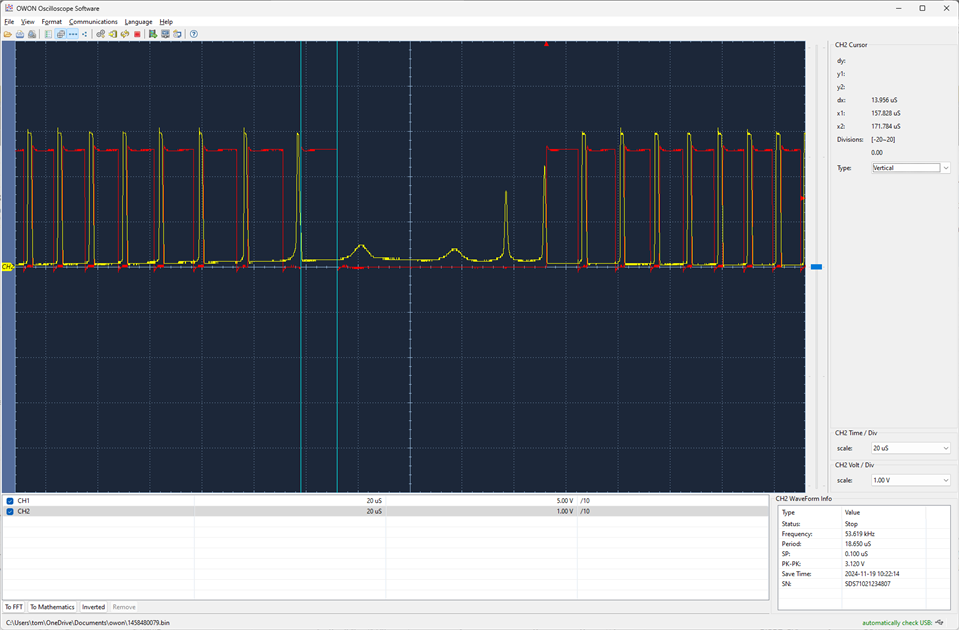

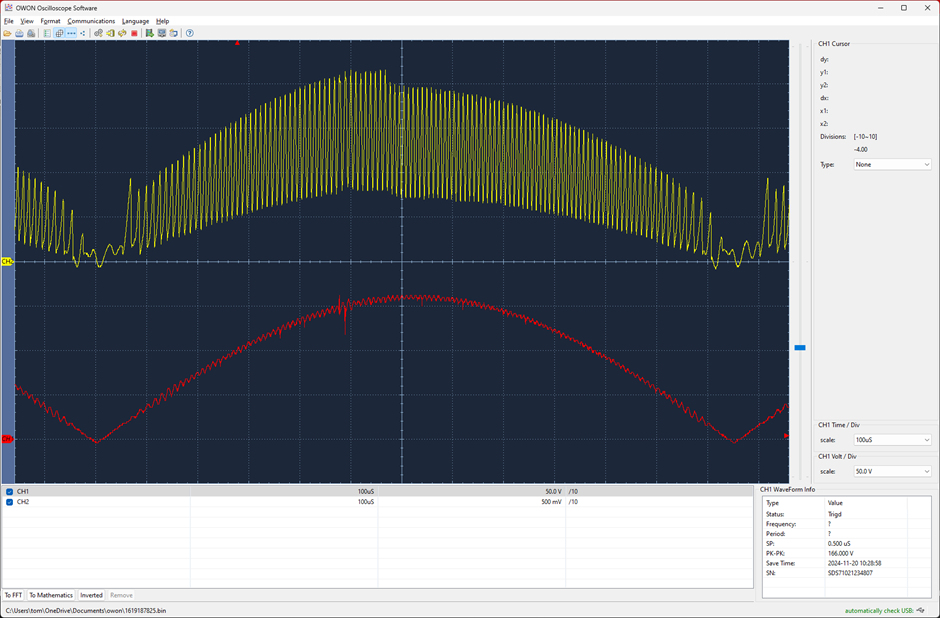

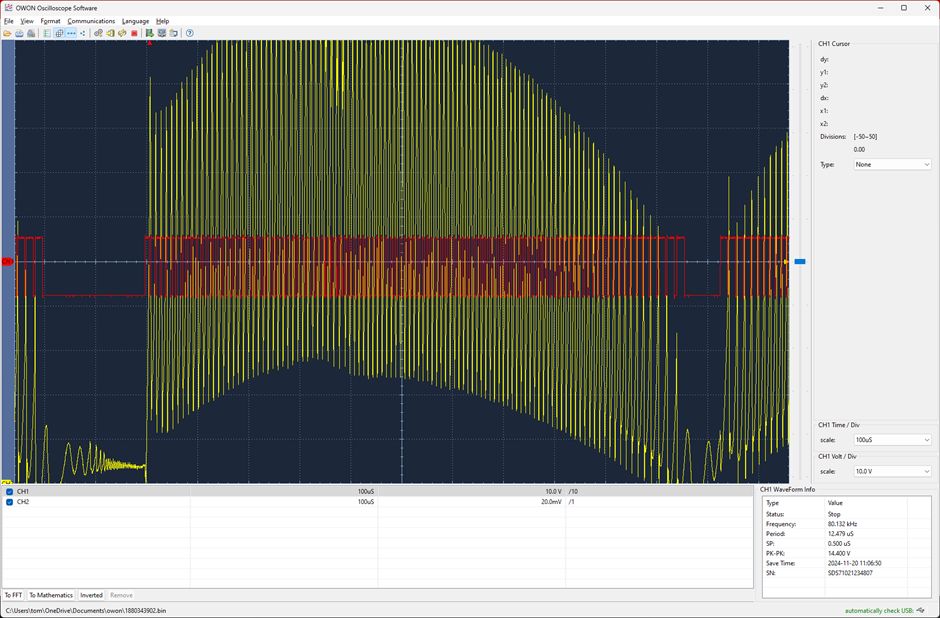

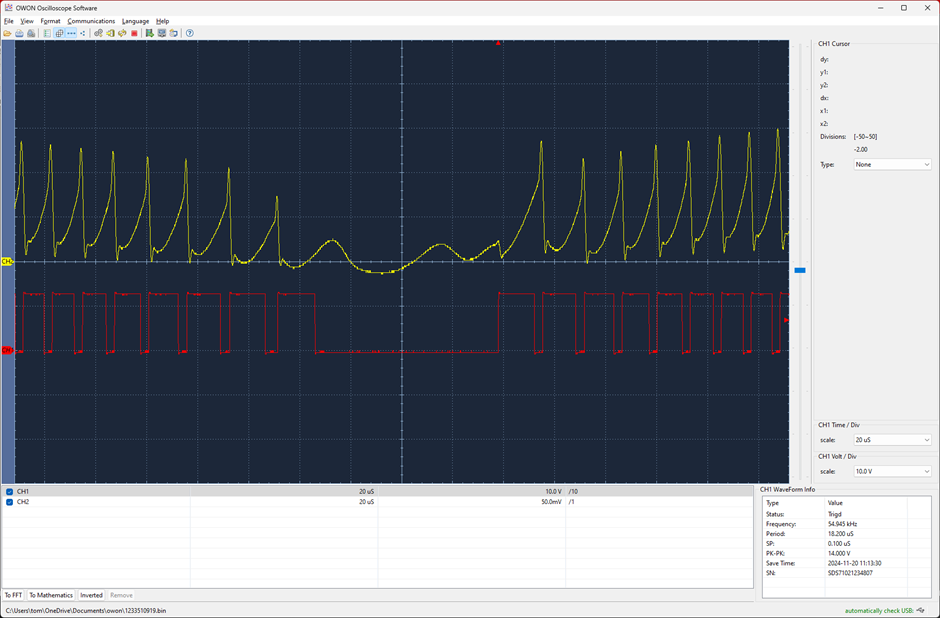

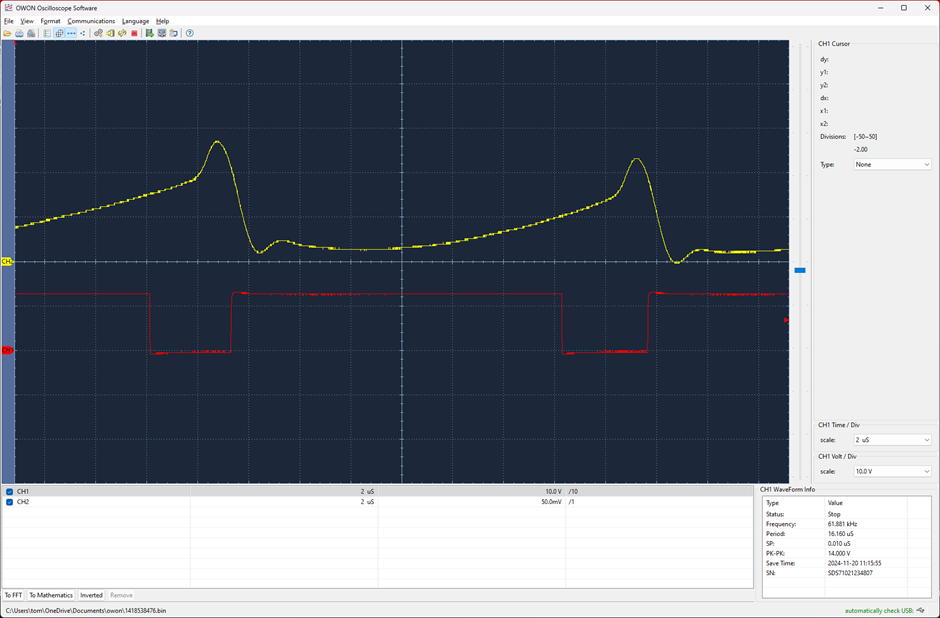

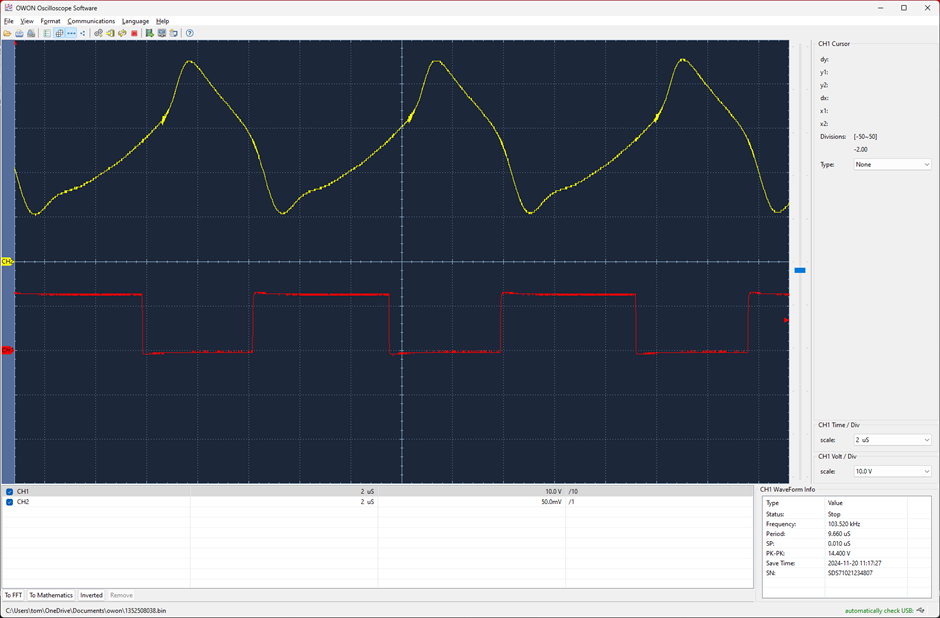

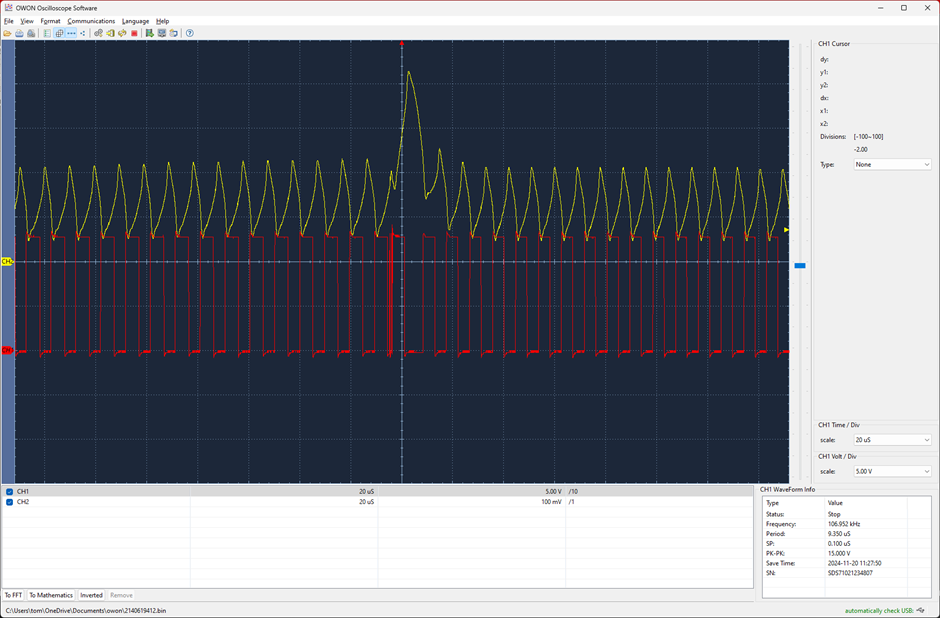

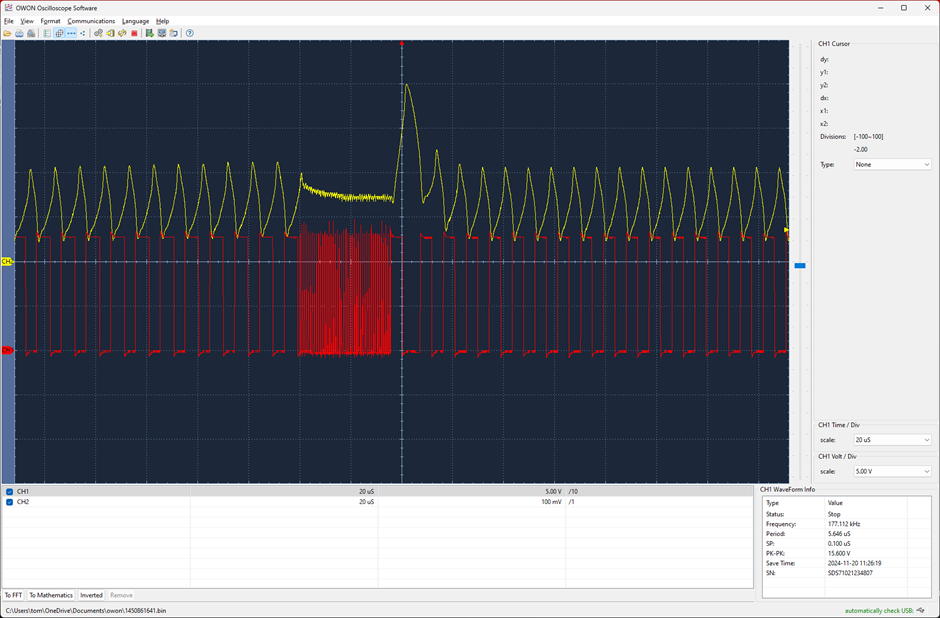

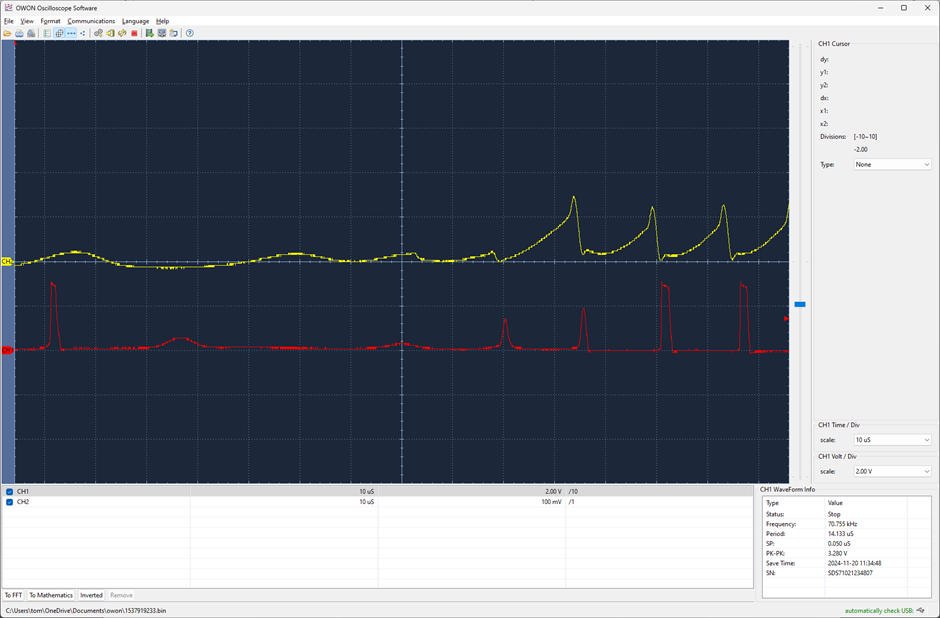

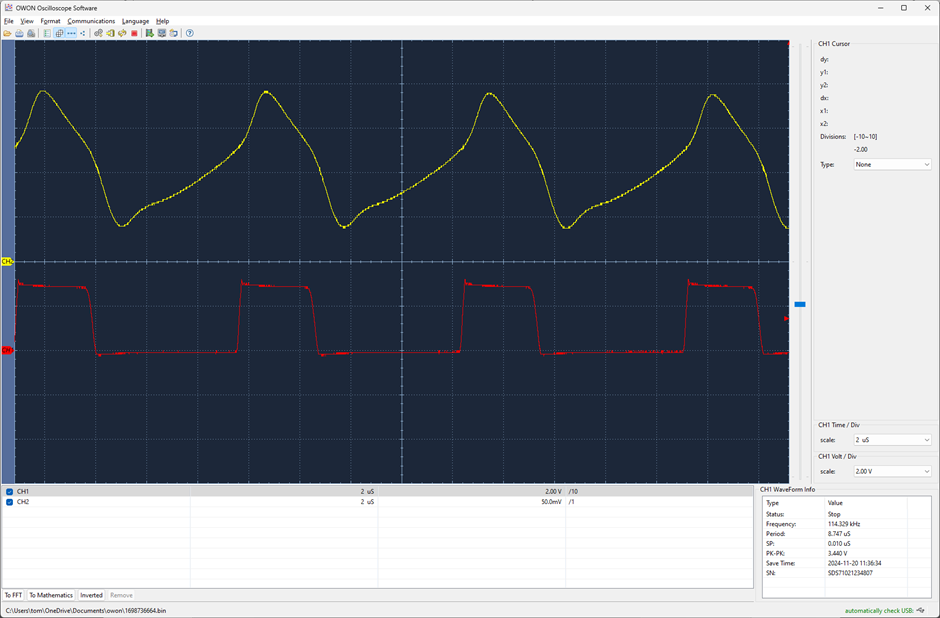

很明显、其意图是近似一致的 PF、所以有些事情是不对的。 在分析开关脉冲后、当 VINAC 信号降至0V 左右时、GDA 和 GDB 输出都停止开关并在 VINAC 在下半个周期上升时再次重新启动。 当开关处于激活状态时、开关时序在半个周期内相当稳定、您可以看到它会随着 VINAC 上升和下降而改变开/关时间。 (目前、我的测试负载是100%电阻性的-一堆加热器元件、让我的脚保持温暖)。

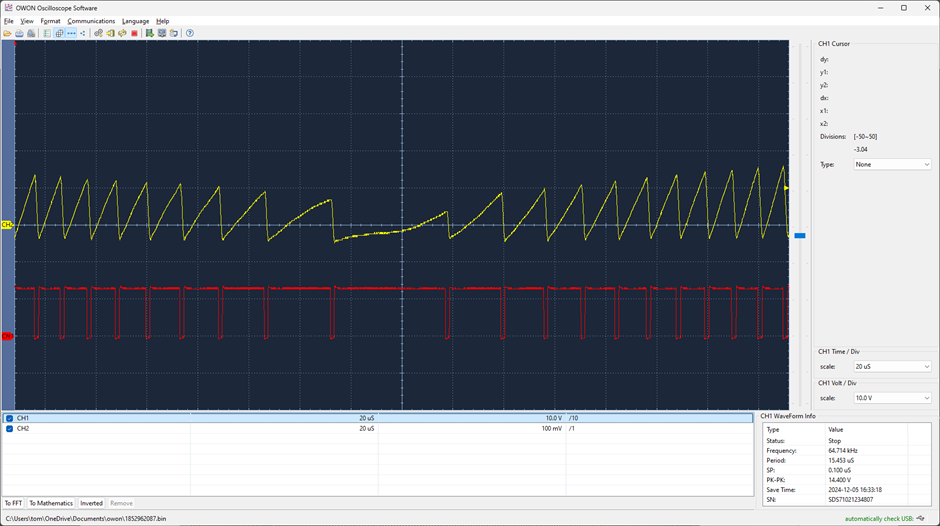

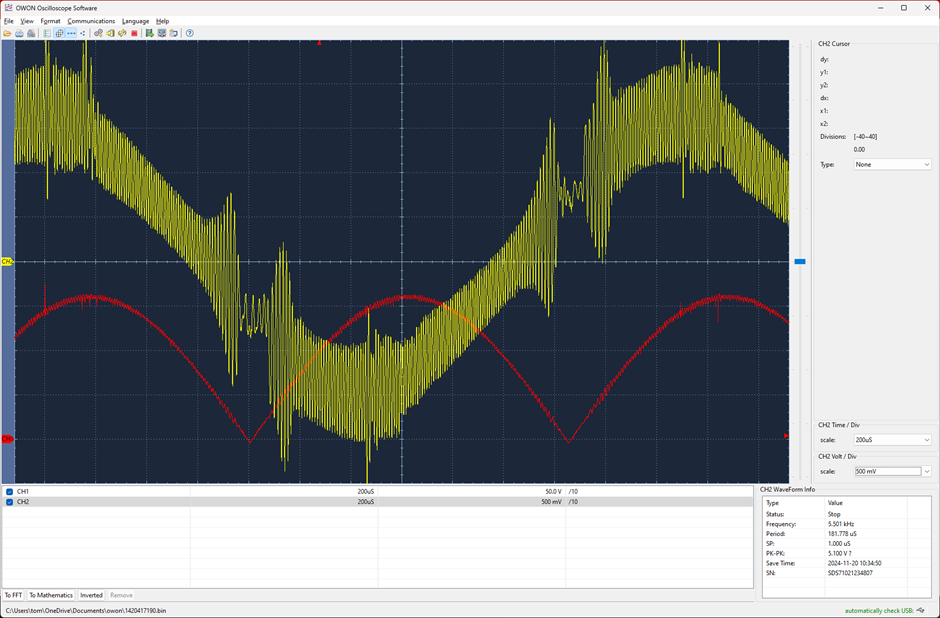

此停止/启动应该预计在0V 点、还是应该在整个周期内继续切换? 此时它们大约在20%的时间处于关闭状态。 重要的是、当开关恢复开启时、它们会彼此同相启动、直到波形接近峰值时才稳定到交错模式、因此我们只在大约40%至50%的时间内以交错模式运行。 这也是人们所期望的吗? 两个相位以同相方式开始?

我已尝试使用/不使用时髦的二极管布置来改善低 VINAC 失真。 没有改进。 我还尝试了启用和禁用 BRST 和 PHB 触发点。 都没有任何效果。

我的电感器目前为250uH、我想知道它们是否太小、因为我必须提高开关频率(增加 RTSET)以防止电流升高。 但是、这里的电感太小会阻止在低 VINAC 下进行开关吗? 将100uH 与它们串联是否是更简单/更明智的解决方案、而不是重新缠绕定制磁性元件?

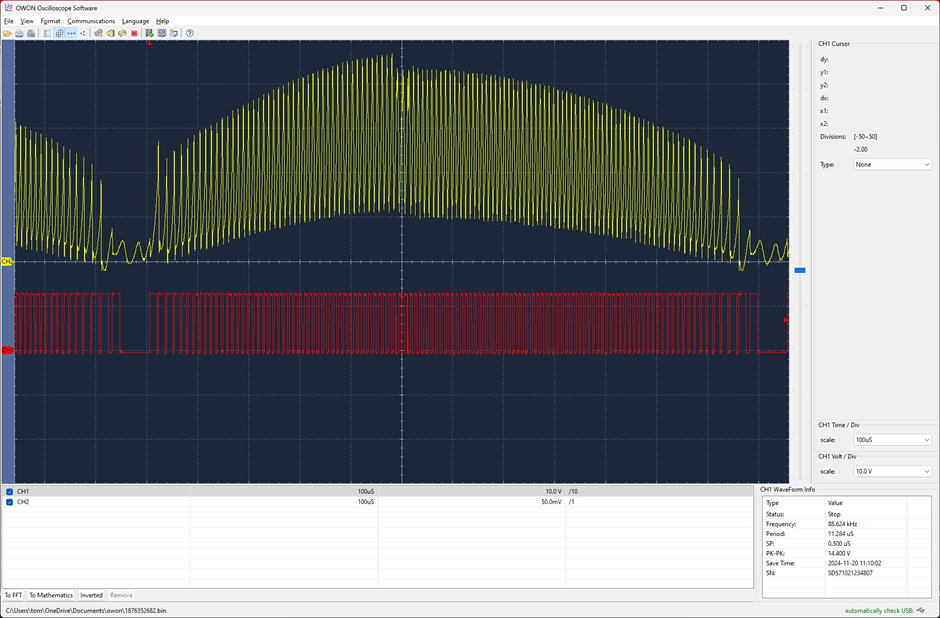

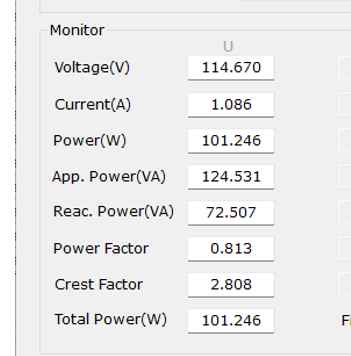

PF 已改进为0.813 (从0.7)

PF 已改进为0.813 (从0.7)