工具与软件:

您好、先生、

晚上好。

我有关于降压转换器死区时间测量和击穿的问题

[问题]

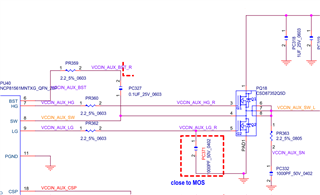

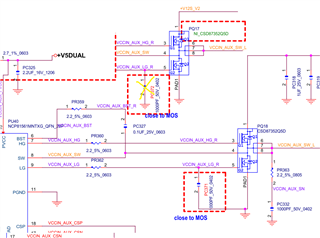

当 LS MOS 关闭-> HS MOS 开启时、我测量 H/L 侧 MOS 栅极波形、观察到它完全重叠

[问题]

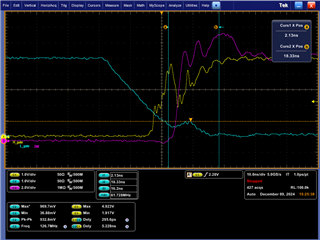

1、我看到 VSW 的波形已经变成了负值, 这是否意味着关断电流进入低侧体二极管? (图1)

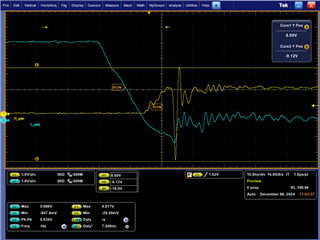

2.当我想调整到更快的 LSMOS 关断时间时、HS MOS Vgs 的振荡效果会比它好 (图2)

我尝试了下面的解决方案

尝试1. LS 栅极电阻降至1R0

尝试2. 删除 Vgs 并联电容

尝试3. HS MOS 栅极电阻添加到3R3、自举电阻添加到3R3

尝试4. 缓冲器更改为1R+472

3.为什么 LS MOS 门看不到在关闭状态下的米勒板? 我猜测这个原因是负电流

4.哪一个波形更好?

您可以帮助提出这个问题,祝您愉快