请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS62A01A-Q1 工具与软件:

尊敬的团队:

我是否知道 VIN<1.8V 时的 PG 引脚行为?

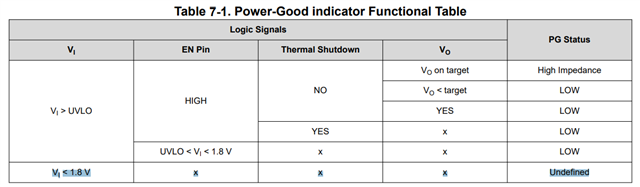

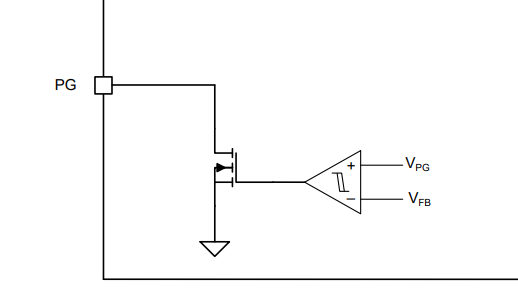

我知道它低于建议的工作范围、因此不能保证达到规格。 表7-1提到了 VIN<1.8V 时、PG 引脚未定义。 根据7.2功能方框图、FET 驱动器比较器将关闭。 那么下拉 FET 将关断。 因此、PG 将处于高阻抗状态、上拉电阻器正常工作、PG 引脚将处于高电平。 我的理解是否正确?

此致、

Yuto Kitamura