Other Parts Discussed in Thread: TPS56C231, TPS56C231EVM

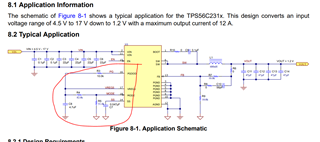

工具与软件:

您好!

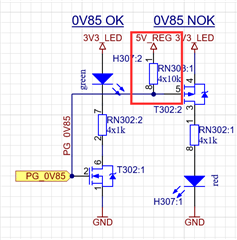

我使用 TPS56C231作为带有其他电压电源的 PCB 上的0V85驱动器。 我有以下电源排序:...->5V_REG ->0V85 ->0V9 ->...

0V9电源通过 TPS56C231 (PG_0V85)的 PG 信号激活

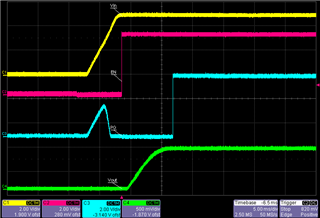

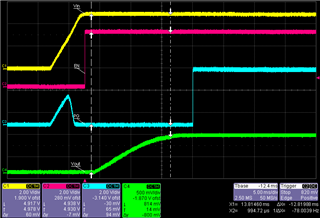

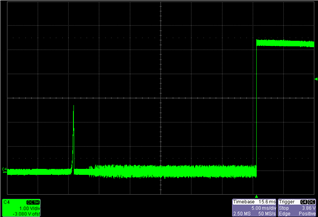

测量结果表明、在0V85导通之前 PG_0V85会出现一个短脉冲:

这会导致短时间启用0V9、这是有问题的。

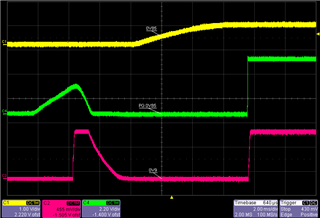

PG_0V85在10k 至5VREG 范围内被拉至高电平:

除了该上拉和与0V9驱动器输入的连接、PG0V85不连接到任何其他位置。

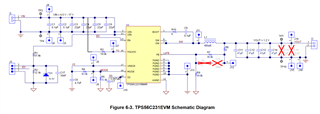

我可以使用评估板 TPS56C231EVM 重现此行为。

我已通过10k 将 PG 连接到 Vin。

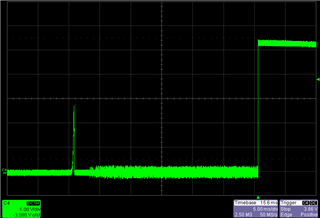

这显示了 PG 上的小脉冲、但事实并非如此。

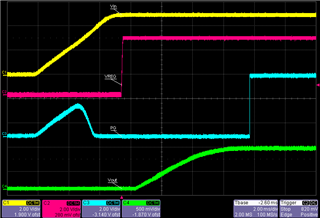

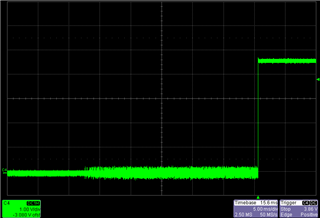

在将 PG 拉高至内部 TPS56C231EVM 电压 VREG5的原始电路中、不会发生该脉冲:

我的简历:

- 电源正常输出被拉至在启用 TPS56C231之前开启的电压-> PG 信号上有故障短路脉冲

- 电源正常 输出被拉至内部 TPS56C231 VREG5 ->预期行为(无脉冲)

这是已知问题吗? 或者我是唯一可以观察到这种脉冲的人吗? 在启动期间是否有一段时间内 PG 输出未定义? 是否必须将 PG 连接到 VREG5?

非常感谢