主题中讨论的其他器件:LMG3100R044、

工具与软件:

大家好、团队成员:

此问题适用于 LMG3100R017和 LMG3100R044。

我在数据表中看到一条注释、"为了根据设计需求灵活地优化死区时间、LMG3100未实现重叠保护功能。" 此外、"必须仔细考虑控制输入以避免击穿情况。"

对于在半桥配置中使用 LMG3100、您是否有关于有效死区时间的指导? 似乎小于100ns 时仍然会导致一些击穿、因此我想看看大家都推荐什么。 提前感谢您的支持。

此致、

Brian

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

工具与软件:

大家好、团队成员:

此问题适用于 LMG3100R017和 LMG3100R044。

我在数据表中看到一条注释、"为了根据设计需求灵活地优化死区时间、LMG3100未实现重叠保护功能。" 此外、"必须仔细考虑控制输入以避免击穿情况。"

对于在半桥配置中使用 LMG3100、您是否有关于有效死区时间的指导? 似乎小于100ns 时仍然会导致一些击穿、因此我想看看大家都推荐什么。 提前感谢您的支持。

此致、

Brian

Brian、您好!

在某些 GaN 器件中、我们整合了击穿保护或锁存输入信号、从而防止两者同时导通。 但是、使用 LMG3100、我们不能通过实现这些特性来实现更灵活的死区时间。

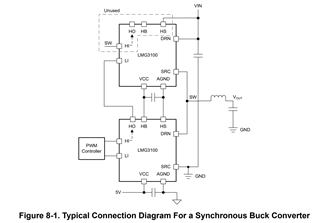

例如、在半桥配置中配置 LMG3100时、客户可以使用集成电平转换从低侧器件同时提供 HI 和 LI 信号、如下所示:

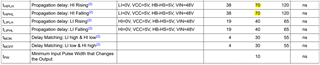

在此配置中、HI 的传播延迟将明显长于 LI、因为信号需要通过电平转换通过低侧器件:

这意味着由于传播失配较高、因此 PWM 信号可实现负死区时间。 FET 实际上不会同时导通、但控制器的信号需要考虑这一点。 一种方法是在大约~30ns 后将低侧信号移位、方法是添加 RC 时间常数以解决高电平信号路径中的额外延迟

LMG3100可轻松实现小于100ns 的死区时间、我们通常建议死区时间至少为8ns 至10ns。 我建议检查低侧和高侧器件 LI 引脚上的信号、以确保按预期施加死区时间。

谢谢!

Zach S